FPGA自动售货机设计:Verilog HDL与QuartusⅡ实现

“verilog hdl自动售货机”

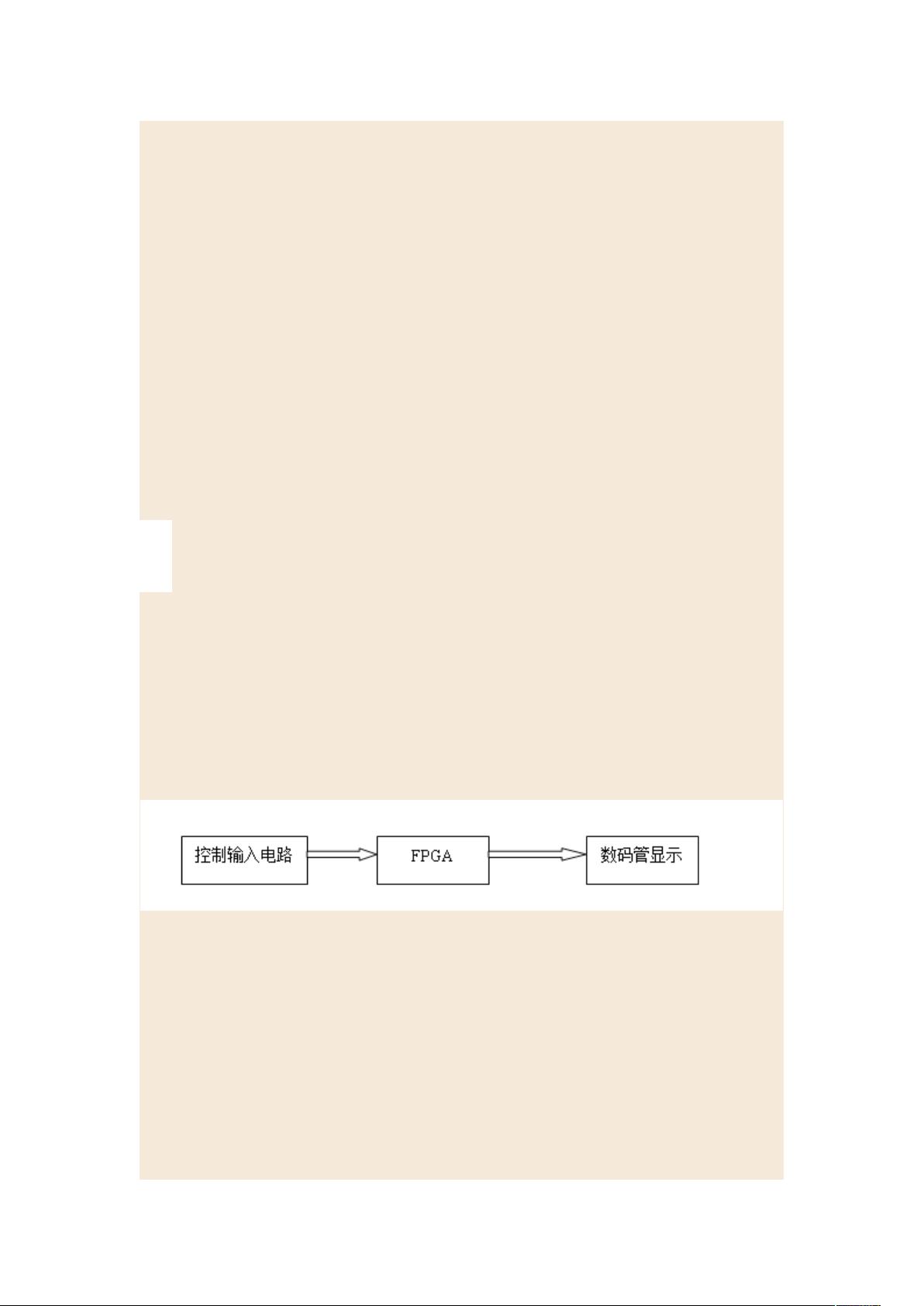

在本次设计中,我们关注的是一个基于Verilog HDL实现的自动售货机系统,该系统利用了现场可编程逻辑器件(FPGA)作为核心处理器。Verilog HDL是一种硬件描述语言,它允许开发者用类似于编程的方式来描述数字系统的硬件行为和结构。在自动售货机的设计中,Verilog HDL被用来编写控制逻辑,以实现自动售货的各种功能。

项目采用了Altera公司的Quartus II软件作为开发环境,这是一款强大的FPGA设计工具,支持Verilog HDL的编译、仿真和综合。通过Quartus II,开发者能够完成设计输入、逻辑优化、配置文件生成等一系列步骤,最终将Verilog代码转化为可以在FPGA上执行的逻辑电路。

自动售货机的硬件接口主要通过实验箱来实现,其中包括了8个开关,它们分别用于设置商品的价格、投入的钱币价值以及确认支付和找零操作。此外,系统还包含了数码管显示模块,用于显示商品价格、已投钱币金额以及找零金额。当用户选择商品并投入钱币后,数码管会显示出相应的信息。如果投入的钱币不足以购买选定的商品,系统会通过警告LED灯提示用户钱款不足。

设计的核心部分是Verilog程序,它包含了以下几个关键模块:

1. 商品选择模块:处理用户选择的商品信息,并根据商品价格设置状态。

2. 钱币接收模块:接收和计算投入的钱币金额,与商品价格进行比较。

3. 支付确认模块:在用户按下确认键后,检查钱款是否足够,如果足够则启动找零计算,否则触发警告信号。

4. 找零计算模块:根据投入的钱币和商品价格计算找零金额。

5. 显示控制模块:驱动数码管显示相关金额信息,以及LED灯状态控制。

6. 声音和灯光反馈模块:当交易成功或失败时,通过蜂鸣器和LED灯提供用户反馈。

这个设计具有很高的教育价值,因为它将理论知识与实际应用相结合,让学生能够亲手实现一个完整的数字系统。通过这样的项目,学习者不仅可以深入理解Verilog HDL语法和FPGA的工作原理,还能掌握硬件设计的基本流程,包括逻辑设计、仿真验证和硬件实现。

总结来说,这是一个利用Verilog HDL和FPGA技术构建的自动售货机系统,它展示了如何使用高级硬件描述语言来描述和实现复杂的数字逻辑。通过实际操作,学习者可以提升其在数字系统设计、Verilog编程以及FPGA应用方面的技能。

2010-12-12 上传

2023-09-14 上传

2024-12-23 上传

2021-03-09 上传

点击了解资源详情

2022-07-13 上传

2021-10-07 上传