FPGA实现的低成本UART设计:优化通信与资源利用

34 浏览量

更新于2024-08-30

收藏 289KB PDF 举报

本文主要探讨了在EDA/PLD(电子设计自动化/可编程逻辑器件)中,如何利用FPGA(现场可编程门阵列)实现高效且经济的UART(通用异步收发器)设计。FPGA因其灵活性、可重构性和低成本的优势,逐渐成为替代传统专用UART芯片的理想平台。

UART作为一种基本的串行通信接口,它支持全双工通信,包括RS232和RS485等多种标准接口,其主要优点在于传输距离远、成本低和可靠性高。然而,传统的专用UART芯片如8250和16450,尽管功能齐全,但其引脚众多且包含许多不必要的辅助功能,这在实际应用中可能导致资源浪费和增加成本。为了简化系统设计并提高效率,将UART功能集成到FPGA中变得尤为重要。

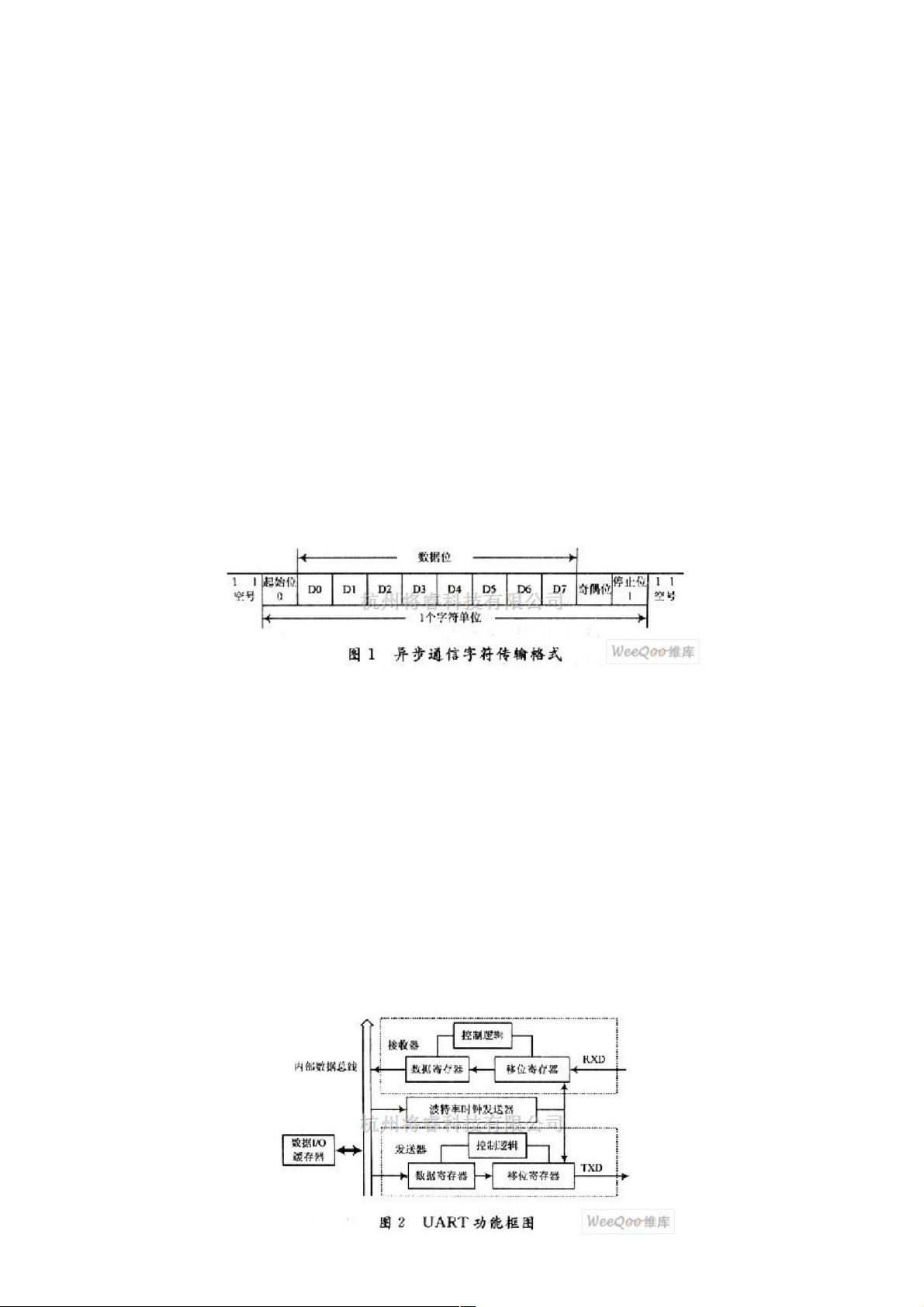

FPGA的设计过程中,首先需要理解UART的基本工作原理。数据的传输遵循特定格式,包括起始位、数据位、可选奇偶校验位以及停止位。发送方通过逻辑“1”变为“0”的跳变信号启动数据传输,接收方则根据这一信号进入同步状态。数据传输后,可选择发送或接收奇偶校验位,最后是一个恒定的停止位。

在FPGA中实现UART,设计师需要配置适当的逻辑电路,如移位寄存器、计数器、比较器等,来模拟UART的时序和逻辑功能。这通常涉及设计发送器,用于生成正确的信号序列;以及接收器,用于正确解析接收到的信号。此外,还需要处理控制信号的同步和错误检测,确保数据通信的可靠性和一致性。

FPGA的可编程特性使得开发者可以根据实际需求定制UART的特性,例如波特率调整、数据位数选择等。这样既避免了专用芯片的冗余,又降低了硬件成本。通过在FPGA上构建一个片上系统,系统集成度提高,开发周期缩短,从而为嵌入式系统和物联网应用提供了一种灵活且高效的解决方案。

总结来说,本文的核心知识点包括UART的工作原理、专用芯片的局限性、FPGA在UART设计中的优势以及在FPGA上实现UART功能的具体步骤和策略。这对于从事嵌入式系统设计或PLD/EDA工作的工程师来说,理解和掌握FPGA的UART设计方法具有重要的实践意义。

157 浏览量

2020-11-05 上传

177 浏览量

162 浏览量

118 浏览量

2020-12-08 上传

147 浏览量

123 浏览量

137 浏览量

weixin_38528888

- 粉丝: 3

最新资源

- 橙色渐变商务科技PPT模板IT产品展示下载

- Camino API:法国数字地籍API的开源实现

- OpenShift Java投资者存储库项目解析

- 浩辰CAD V2019二次开发SDK支持与技术支持指南

- 服务器运维全套客户端源码资源下载

- 深入探讨Vue.js项目开发实践

- 新天龙八部电脑主题 xp版安装指南与体验分享

- 新年祝福主题的金玉满堂PPT模板下载

- myPortfolio项目开发与配置指南

- Unitizer:Java BigDecimal单位转换的简便方法

- R语言项目:压缩包子文件操作详解

- 利用JupyterNotebook进行高效日常学习

- 绿色植物背景PPT模板下载-叶子上的露珠

- Java开发必备:解析dom4j-2.0.2的使用与下载

- STM32F103在EMWin中实现中文显示的方法

- wang-cli:打造高效的个人JavaScript开发环境