S3C2443处理器时钟管理详解与编程设置

需积分: 9 30 浏览量

更新于2024-09-09

收藏 174KB DOCX 举报

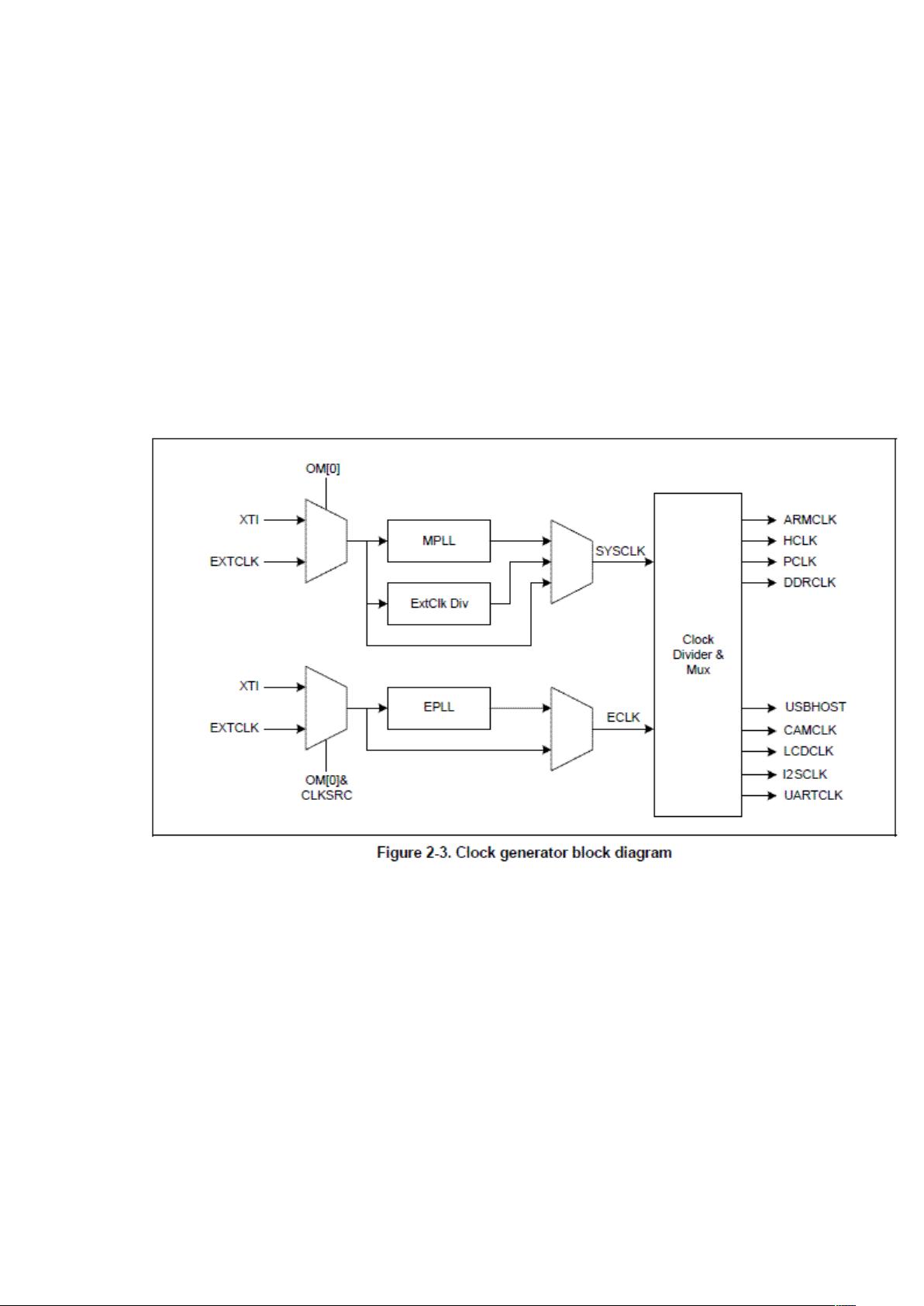

S3C2443是一款由三星公司开发的嵌入式微控制器,它具备高效的时钟管理系统,这对于保证处理器内部各个模块的稳定运行至关重要。该处理器的时钟管理主要通过两个PLL(Phase-Locked Loop,锁相环)来实现,即Main PLL (MPLL) 和 External PLL (EPLL)。

MPLL负责为处理器的主要功能模块如ARM内核、AHB总线以及APB总线提供时钟,它的时钟源选择可以从外部晶振XTI或外部时钟EXTCLK中选取。在实际应用中,MPLL的时钟源由硬件设计决定,例如在提供的项目设计中,OM[0]寄存器的配置使MPLL选择XTI作为时钟源。而EPLL则用于为特定模块,如USB、I2S和相机接口等提供时钟,由于EXTCLK直接接地,EPLL只能利用XTI作为输入时钟源。

PLL的工作原理涉及到多个组件:PFD(相位差检测器)负责检测输入信号与输出信号的相位差异并将其转换为电压信号;Chargepump则将PFD的电压信号放大,以便驱动VCO(电压控制振荡器)。VCO是核心组件,其输出频率受输入电压控制,当输入电压稳定,且与参考频率Fref相匹配时,PLL锁定,PFD停止输出电压,从而确保系统的时钟精度。

Off-chip loop filter是一个外部环路滤波器,它对于去除PFD输出信号中的高频噪声至关重要,通过经典的RC低通滤波技术,提供给VCO一个稳定的工作电压环境。通过精细调整这些PLL组件,开发人员可以根据需求动态调整MPLL和EPLL的工作频率,从而在满足系统性能的同时优化功耗。

在S3C2443的初始化阶段,如startup.s文件中,开发者需要设置CLKSRC寄存器来配置PLL的工作模式,确保各个模块能正确获取所需的时钟。理解并熟练掌握时钟管理对于S3C2443的编程和优化至关重要,因为良好的时钟管理不仅影响系统性能,还直接影响到设备的功耗管理和整体稳定性。在实际项目中,开发者需要灵活运用这些知识,根据硬件配置和应用需求进行适当的时钟配置。

2008-12-13 上传

2022-09-22 上传

点击了解资源详情

2022-09-14 上传

2022-09-19 上传

2022-09-19 上传

2009-03-31 上传

2010-11-10 上传

2022-09-19 上传

loongembedded

- 粉丝: 2434

- 资源: 16

最新资源

- Oracle数据库10g与DB2比较

- 吉林大学,最全的Java工作流资料

- 70-547: PRO: Designing and Developing Web Applications by Using the Microsoft .NET Framework

- SQL2008基础教程

- sniffer教程 最新的sniffer教程 sniffer基础学习

- tuxedo开发说明

- tuxedo配置说明

- asp.net常用函数表

- AJAX开发简略——非常好的AJAX开发资源

- USB转串口转换器用户手册

- 70-316基于C_的Windows应用程序设计(四套)

- C_的Framework程序设计_answer

- C++ Standard library

- 将DW数据窗口导出为EXCEL文件的方法(整理)

- 基于灰色系统理论的自贡旅游需求预测与分析

- Linux必学的重要命令教程