FPGA内LPM存储器:ROM/RAM设计与应用优势

需积分: 36 133 浏览量

更新于2024-07-16

收藏 1.41MB DOCX 举报

在计算机组成原理的学习中,本实验主要围绕LPM存储器在FPGA(Field-Programmable Gate Array,可编程逻辑阵列)中的应用展开。LPM存储器,即Look-Up Table Memory,是一种嵌入在FPGA内部的高速可编辑存储单元,因其与FPGA的JTAG接口(Joint Test Action Group)独立通信,提供了极大的灵活性和效率。通过这种存储器,我们可以方便地实现ROM(Read-Only Memory,只读存储器)和RAM(Random Access Memory,随机存取存储器)的功能,用于数据存储、程序执行以及其他关键任务。

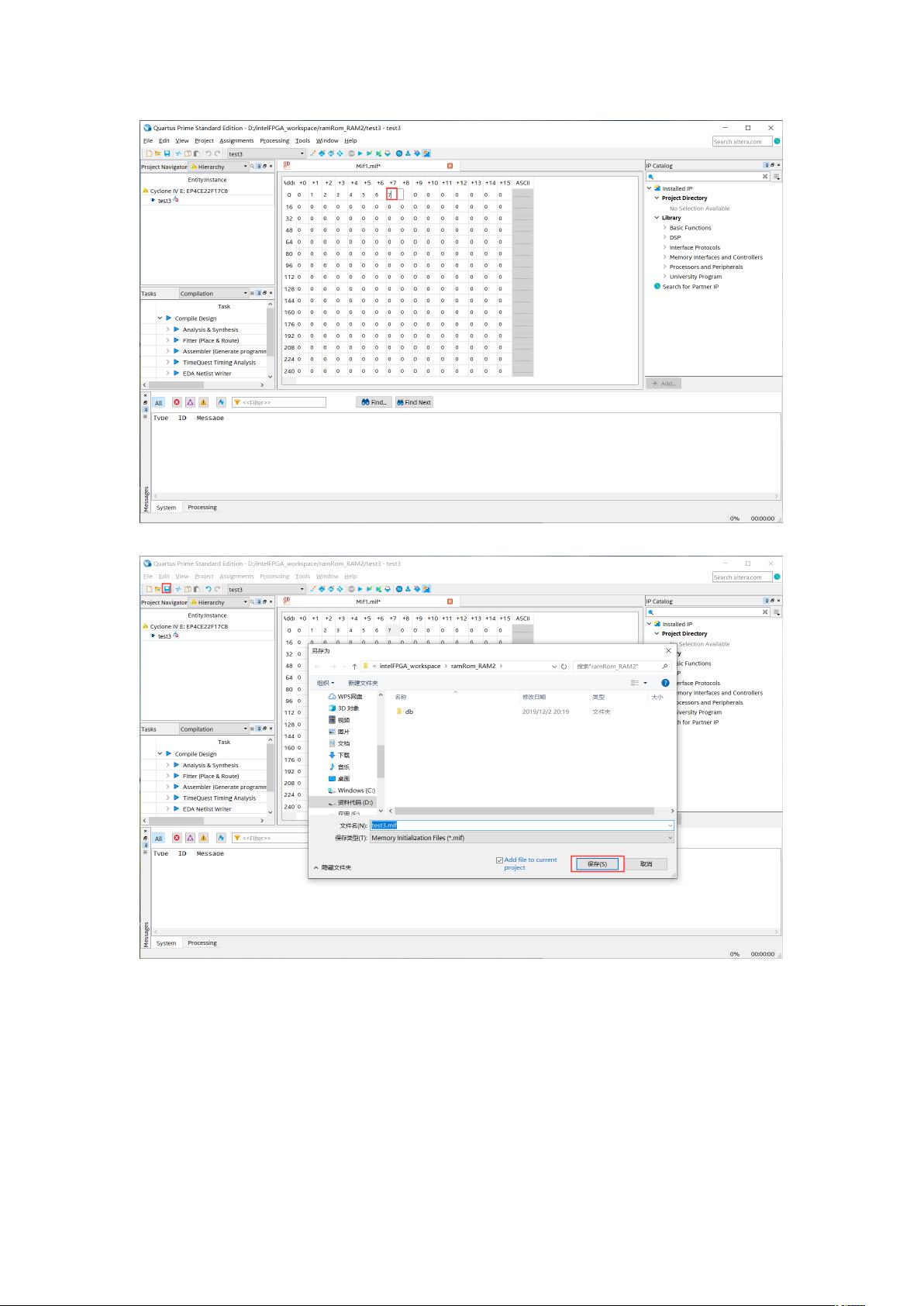

首先,实验开始时需要新建一个工程,保持与以往相同的步骤,但这里特别提到可以调整字宽,老师建议使用32位,尽管老师之前使用的是8位。创建MIF(Memory Initialization File,初始化文件)来配置存储器,MIF是描述FPGA存储器配置的文本文件。

接下来,设计RAM时,选择1端口类型,设置32位宽。在内存结构中添加额外层次的路径,以便更好地组织和管理数据。为了实现无时钟控制的输出,需要取消某些选项以让Q端口的输出不受时钟信号CLK的影响。

在配置过程中,选择先前创建的MIF文件并导入,同时指定独特的ID。随后的步骤包括配置其他参数,如是否启用特定功能(.bsf选框)以及设置仿真参数,如时间格式(改为微秒)和初始值。对于地址寄存器(ADR),可以根据显示需求进行适当调整,4地址线可能足以满足大部分实验场景。

进行对比试验时,可以修改WREN(Write Enable)寄存器,这可能影响存储器的写操作权限。实验最后验证了这些设置的有效性,因为导师已经亲自测试并确认了结果。

这个实验强调了FPGA LPM存储器在现代计算机系统设计中的实用性和定制性,特别是如何通过灵活的配置和接口设计,实现高性能、高效能的存储器模块。通过实践,学生可以深入理解ROM和RAM在FPGA中的工作原理,以及如何利用LPM技术优化存储器性能。

2057 浏览量

171 浏览量

2022-07-10 上传

600 浏览量

641 浏览量

362 浏览量

356 浏览量

sticker_start_tag

- 粉丝: 104

最新资源

- Java开发手册:高清中文版及详细目录解析

- Gulp命名模块:简化前端未命名Require模块管理

- JavaScript实现经典贪吃蛇游戏教程

- 在线考试系统2.7.7版本全面升级,功能更强大

- STM32F303基础工程文件详解

- 江南红月游戏服务器端及GM工具源码发布

- FFXIV开瓶器制作指南与在线应用介绍

- Azure API管理动手实验室:研讨会指南

- jeecg-boot 2.1实现在线表单与Vue路由页面集成

- API测试示例实践:深入解析HTML应用

- pwatools: 快速构建跨平台PWA的JavaScript库

- IPL数据集探索性数据分析深度解读

- 构建.NET Core MVC与EF Core集成Demo

- Android应用实现滑动刷新功能的示例教程

- VCE文件打开工具v3.1注册版安装与使用教程

- Fullstaq Ruby Server Edition:高效内存管理与快速安装的Ruby发行版