高性能32位移位寄存器单元设计与优化

198 浏览量

更新于2024-08-30

收藏 144KB PDF 举报

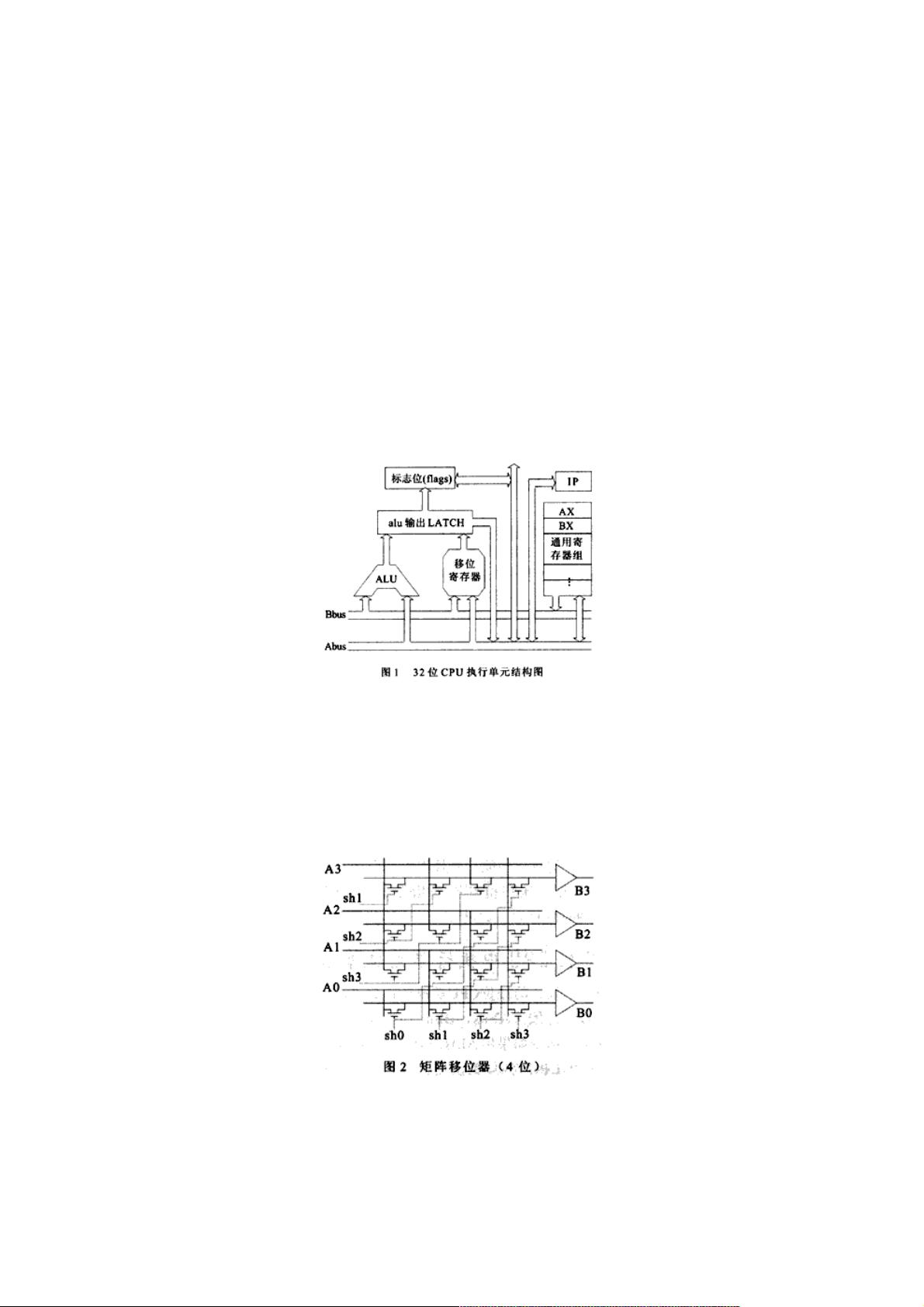

"本文主要介绍了一种针对32位及以上CPU执行单元的高性能移位寄存器设计,特别优化了INTEL X86架构下的CISC指令集,以提高移位指令的执行效率。设计中采用了指令预处理技术和冗余位来支持带进位标志CF的移位操作,并确保每条移位指令的平均执行速度为两个指令周期。文章还探讨了矩阵移位器和树状移位器两种常见的移位器结构,并分析了它们的优缺点。"

在计算机硬件设计中,移位寄存器是一种关键组件,尤其对于32位或更高位宽的CPU而言,它在执行单元中的作用至关重要。本文提出的移位寄存器设计专注于提升性能,以适应CISC(复杂指令集计算)架构的INTEL X86指令集,因为RISC(精简指令集计算)架构的移位指令通常较简单,不在此文中详述。

为了优化INTEL X86的移位操作,设计中利用了指令预处理技术,这允许在执行移位指令前预先处理数据,以减少执行时间。同时,通过引入冗余位,可以方便地处理进位标志CF的设置,这对于执行像RCR(带进位循环右移)、RCL(带进位循环左移)、ROR(无符号循环右移)和ROL(无符号循环左移)等指令至关重要。通过这种方式,每条移位指令的平均执行速度得以提升至两个指令周期,显著提高了处理器的效率。

在硬件实现上,32位CPU的执行单元采用双总线结构,数据总线分为Abus和Bbus,两者均为32位宽。移位寄存器作为一个专用硬件,设计为双输入,最大可实现64位移位,以覆盖INTEL X86指令集的所有移位需求。移位寄存器的控制逻辑通过特殊的方法设置,以处理各种移位操作,并通过冗余位处理标志位的更新,保证了指令执行的精确性。

文章进一步讨论了两种常用的移位器结构:矩阵结构移位器和树状结构移位器。矩阵结构移位器以其快速的数据传输和规整的布局而著称,但其控制信号负载大、晶体管数量多、功耗和面积占用增加的问题也不容忽视。而树状结构移位器则可能在某些方面提供更好的解决方案,例如降低控制信号的负载,但它可能牺牲一部分速度。

本文提出的32位移位寄存器设计结合了指令预处理和冗余位的概念,以优化CISC指令集的执行,同时考虑了硬件实现的效率和成本,为高性能CPU设计提供了有价值的参考。

367 浏览量

136 浏览量

158 浏览量

106 浏览量

236 浏览量

224 浏览量

2023-06-09 上传

weixin_38706045

- 粉丝: 4

- 资源: 950