优化FPGA设计:TimeQuest时序分析的关键

需积分: 9 105 浏览量

更新于2024-08-01

收藏 1.28MB PPT 举报

"FPGA设计的代码风格与时间分析"

在FPGA设计中,代码风格扮演着至关重要的角色。良好的代码风格不仅能够使设计更加优化,提高效率,还能帮助开发者避免在设计过程中走弯路。本资源主要探讨了如何在FPGA设计中采用最佳的编码实践,以实现更高效、更可靠的逻辑功能。

FPGA设计通常涉及到硬件描述语言(如VHDL或Verilog)的使用,代码风格在此类设计中的重要性不亚于软件开发。良好的代码风格可以提高代码的可读性、可维护性和可重用性,使得团队协作更为顺畅,同时也有助于工具(如Altera的Quartus II)进行更有效的综合和时序分析。

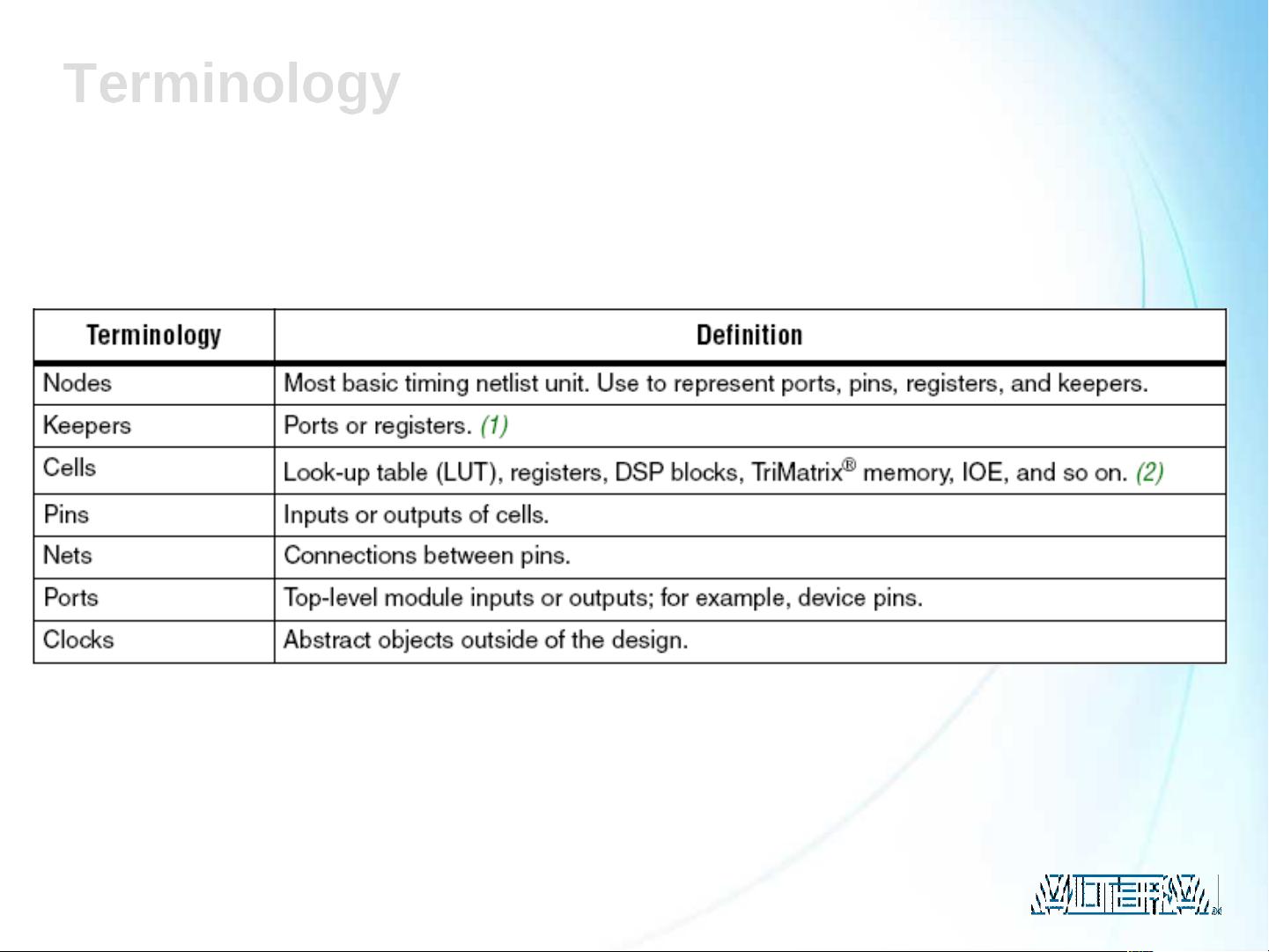

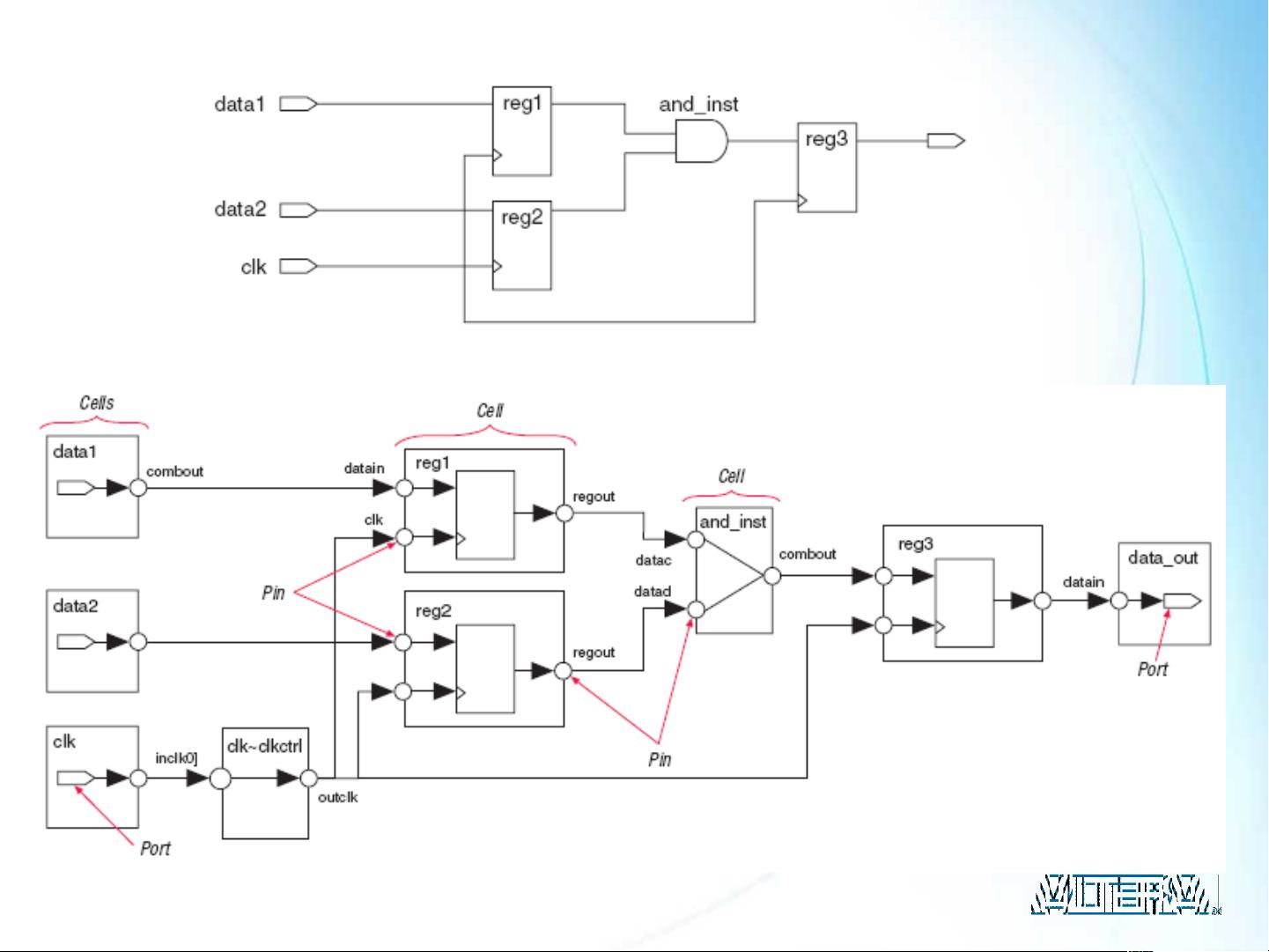

Quartus II是一款广泛使用的FPGA设计套件,其中的时间分析器TimeQuest是评估设计时序性能的关键工具。TimeQuest提供了比传统时序分析器更高级的功能,以应对现代FPGA设计的复杂性。TimeQuest术语审查涵盖了诸如路径延迟、时钟约束、I/O约束等核心概念,这些都是确保设计满足速度目标的关键因素。

TimeQuest与经典的时序分析器的主要区别在于其处理设计复杂度的能力。随着FPGA设计的复杂度和FPGA本身集成度的提升,简单的时序分析已无法满足需求。TimeQuest引入了先进的时序分析技术,能够处理深度嵌套的逻辑、多时钟域以及复杂的时序约束。

设计流程与TimeQuest的结合使用是确保设计满足时序要求的关键步骤。这包括在设计初期设定合适的时钟、I/O和高级SDC(时序设计约束)约束,通过TimeQuest进行时序分析,然后根据分析结果进行迭代优化。TimeQuest的演示部分可能详细展示了如何使用该工具进行这些操作。

在TimeQuest中,对时钟、I/O和高级SDC约束的深入理解至关重要。时钟约束定义了系统中不同部分的同步方式,I/O约束则影响着输入输出信号的速度和时序行为。高级SDC约束允许设计者精确地指定时序要求,例如设置特定路径的延迟限制,这对于高速通信和实时系统的时序管理尤其重要。

FPGA设计的代码风格直接影响到设计的质量和效率,而TimeQuest作为强大的时序分析工具,可以帮助开发者应对日益复杂的设计挑战。通过遵循最佳编码实践,结合TimeQuest的高级分析功能,可以确保FPGA设计达到预期的性能指标,同时降低设计风险。

2019-08-26 上传

2021-07-09 上传

点击了解资源详情

2018-04-04 上传

2013-09-15 上传

2023-03-01 上传

2018-02-10 上传

2009-03-31 上传

2010-02-27 上传

guoqiang2

- 粉丝: 0

- 资源: 3

最新资源

- C语言快速排序算法的实现与应用

- KityFormula 编辑器压缩包功能解析

- 离线搭建Kubernetes 1.17.0集群教程与资源包分享

- Java毕业设计教学平台完整教程与源码

- 综合数据集汇总:浏览记录与市场研究分析

- STM32智能家居控制系统:创新设计与无线通讯

- 深入浅出C++20标准:四大新特性解析

- Real-ESRGAN: 开源项目提升图像超分辨率技术

- 植物大战僵尸杂交版v2.0.88:新元素新挑战

- 掌握数据分析核心模型,预测未来不是梦

- Android平台蓝牙HC-06/08模块数据交互技巧

- Python源码分享:计算100至200之间的所有素数

- 免费视频修复利器:Digital Video Repair

- Chrome浏览器新版本Adblock Plus插件发布

- GifSplitter:Linux下GIF转BMP的核心工具

- Vue.js开发教程:全面学习资源指南