Quartus II 10.0入门教程:Verilog设计与FPGA实现流程详解

需积分: 10 177 浏览量

更新于2024-07-20

收藏 1.01MB DOCX 举报

Quartus II 10.0教程是一份针对 Altera FPGA 开发者的全面指南,主要使用软件Quartus II 10.0与ModelSim-Altera 6.5e Starter Edition。该教程覆盖了典型的FPGA CAD(计算机辅助设计)流程,包括以下几个关键步骤:

1. **设计输入**:首先,用户可以使用原理图或硬件描述语言(如Verilog)创建所需电路的设计。Verilog是首选的语言,它允许开发者以文本形式描述数字逻辑行为。

2. **综合**:将Verilog设计输入到Quartus II,软件会将其转换为由FPGA芯片内部逻辑元素(LEs)构成的实际电路,这个过程称为综合。

3. **功能仿真**:完成综合后,对电路进行功能仿真,确保逻辑功能正确,但不涉及时序分析。

4. **布局布线**:CADFitter工具负责优化LE的布局,将网表定义映射到实际FPGA芯片上的LE位置。

5. **时序分析**:分析电路的延迟,以评估其性能并优化设计。

6. **时序仿真**:在布局布线后的阶段,进行时序仿真,再次确认电路在功能和时间上均符合预期。

7. **编程及配置**:最后,通过编程配置将设计的电路加载到FPGA芯片中,这通常涉及设置LEs的状态和连接。

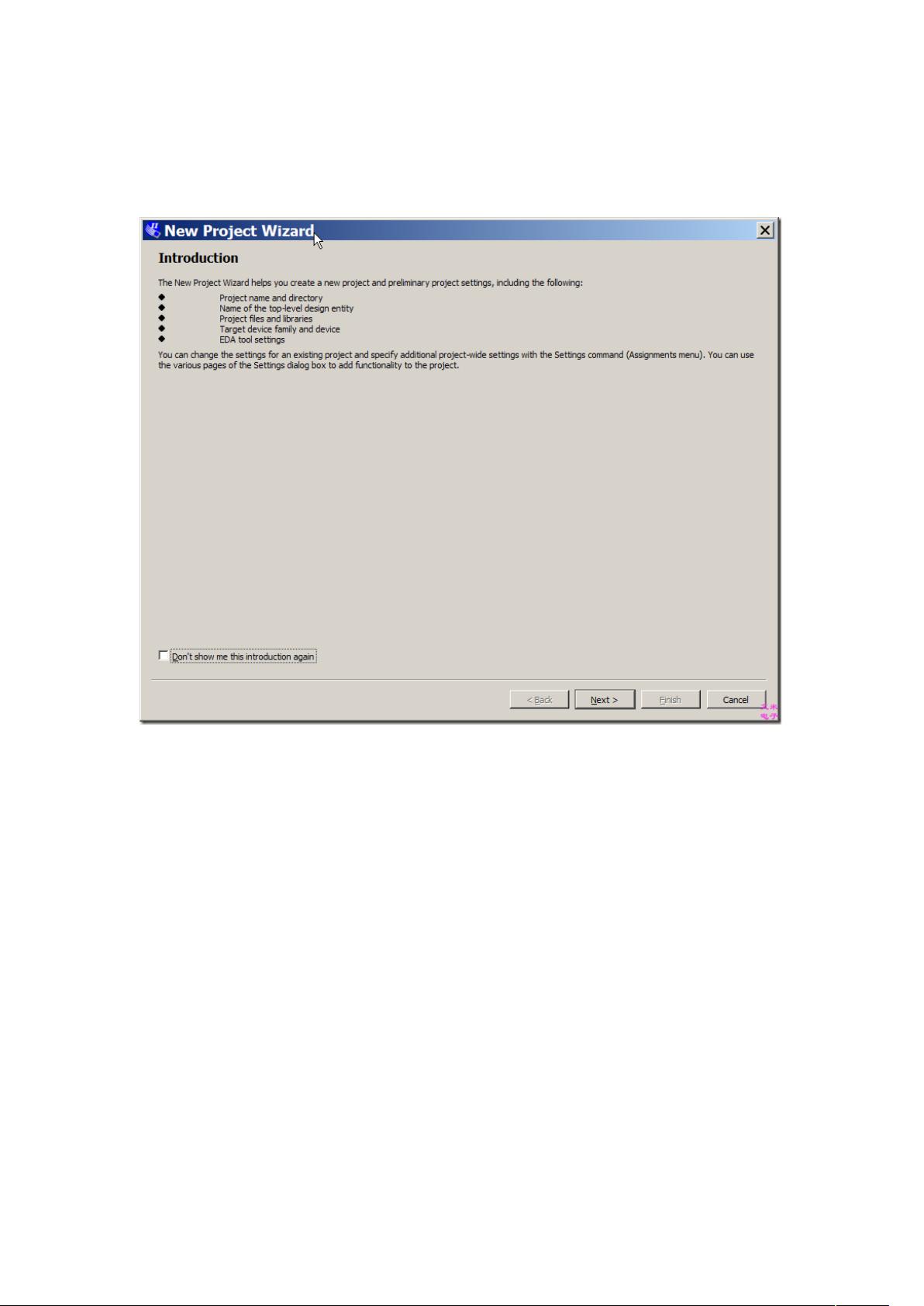

教程详细介绍了如何在Quartus II中操作,例如新建工程、使用Verilog代码编写设计、布局电路至Altera FPGA、分配I/O引脚以及在艾米电子EP2C8核心板上编程配置FPGA。整个过程中,用户会通过图形用户界面(GUI)进行操作,以便于理解和实践。

在整个设计流程中,每个新项目都会在单独的工作目录下进行,便于管理和版本控制。对于新手来说,这份教程尤其实用,因为它不仅教授技术知识,还提供了具体的实例,如双路灯控电路的设计和实现,帮助用户逐步掌握FPGA开发的基本技能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2015-12-21 上传

2011-02-12 上传

2020-03-31 上传

963 浏览量

2010-11-05 上传

chengjunbeili

- 粉丝: 0

- 资源: 1

最新资源

- Linux+cramfs文件系统移植

- linux与unix shell编程指南

- jsp高级编程 进阶级

- C语言开发环境的详细介绍

- PIC单片机伪指令与宏指令

- linux下jsp apache tomcat环境配置

- 基于TMS320F2812的三相SPWM波的实现

- matlab神经网络工具箱函数

- microsoft 70-536题库

- 计算机英语常用词汇总结

- 嵌入式C/C++语言精华文章集锦

- 嵌入式uclinx开发

- CRC32真值表,很多想想要,我发下

- flutter_nebula:Flutter nebula是Eva设计系统的一个Flutter实现

- pyg_lib-0.2.0+pt20-cp311-cp311-macosx_10_15_universal2whl.zip

- react-native-boilerplate:适用于具有React-Native + React-Navigation + Native-Base + Redux + Firebase的项目的样板