组合逻辑电路设计详解:功能分析与实用教程

下载需积分: 20 | PDF格式 | 527KB |

更新于2024-09-10

| 91 浏览量 | 举报

组合逻辑电路的设计是数字电路设计中的一个重要部分,它主要关注于在特定时刻电路的输出仅依赖于当前的输入状态,而不受先前状态的影响。这种电路结构基于门电路,如与门、或门、非门等,不包含任何形式的记忆单元(如触发器),因此输出与输入之间的关系是直接且无延迟的。

在组合逻辑电路的设计过程中,有四个关键环节:

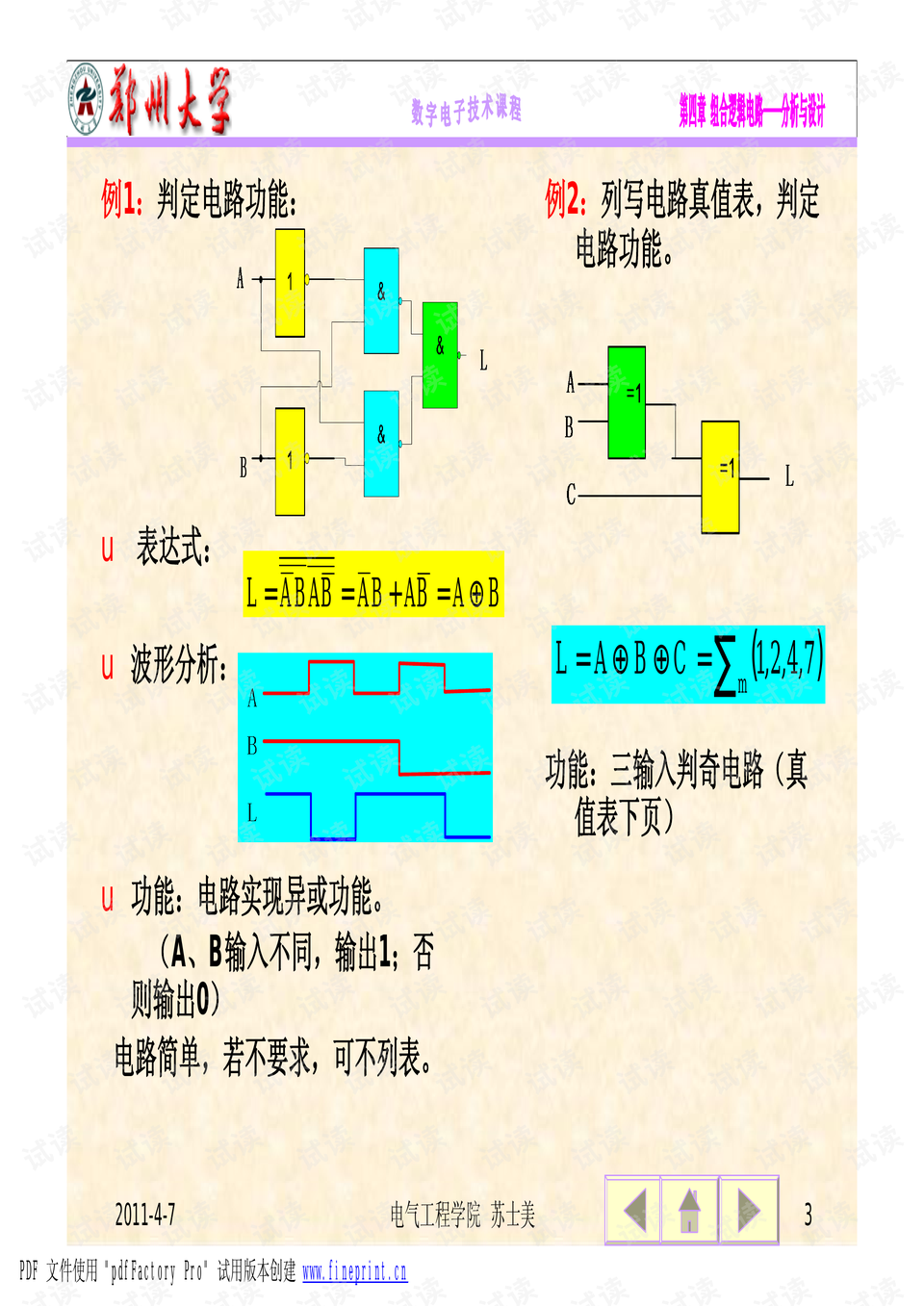

1. 电路分析:首先,需要理解并分析电路的功能需求,这通常通过逻辑表达式、真值表、卡诺图或逻辑图来实现。例如,通过例1中的异或函数,可以看出输入A和B的不同会导致输出为1,反之为0。

2. 功能描述:除了逻辑表达式外,还可以用真值表来直观展示所有可能输入组合对应的实际输出结果,如例2中的三输入判奇电路,通过真值表可以清晰地看到电路是否能正确判断输入的奇偶性。

3. 设计步骤:一旦逻辑要求明确,设计者会遵循一定的步骤进行:a) 分析逻辑需求,定义输入和输出变量;b) 依据这些变量制作真值表;c) 将真值表转化为逻辑表达式,选择合适的门电路或集成逻辑器件,如编码器、译码器、数据分配器等;d) 对表达式进行简化,并绘制出实际的逻辑电路图。

4. 典型器件:组合逻辑电路中常见的集成器件包括编码器,将二进制代码转换为不同的输出信号;译码器,反之亦然;数据分配器用于将单个输入信号分配到多个输出端;数据选择器则是根据某些控制信号决定数据流的方向;比较器用来比较两个或多个输入;加法器则是执行简单的算术运算。

组合逻辑电路的设计强调的是即时反应和确定性,这对于许多应用场合至关重要,如数据处理、逻辑控制、信号处理等。在选择器件时,设计者需考虑成本、功耗、速度等因素,以及可能存在的竞争冒险现象,即因电路结构导致的输出错误。通过对逻辑电路的深入理解和设计,工程师能够创建高效、可靠和易于维护的电子系统。

相关推荐

蒲建波

- 粉丝: 0

最新资源

- 基于MATLAB的学生管理系统代码实现与研究应用

- 3D图片切换效果:网页模版中的视觉盛宴

- 解决JDK 13.0.1下载速度慢的高效替代方案

- Winform中嵌套子报表的RDLC实现方法

- 超市管理系统毕业设计:完整文件包括论文与演示

- 创建自定义页面提示三角形的JavaScript方法

- 32位环境下可用的QuaZIP编译库文件

- 快速下载JDK 8u231 Windows x64官方安装包

- Windows环境下MASM5.0汇编开发工具的使用

- Papervision3D: 开源Flash 3D Web应用的革命

- C# Winform皮肤控件IrisSkin2.dll使用指南

- ZigBee协议分析仪软件Packet Sniffer详解

- 范伟sniffer教程:网络嗅探基础知识与应用

- 办公室3D模型设计:老总办公室模型详细解析

- MATLAB学生管理系统:CS5200课程项目代码分析

- 深入讲解Maven多模块项目构建技巧