FPGA时钟资源设计与实现

需积分: 10 200 浏览量

更新于2024-07-20

收藏 1.58MB PPT 举报

FPGA片上可编程系统设计(时钟资源)

FPGA(Field-Programmable Gate Array)片上可编程系统设计是指通过编程来实现数字电路的设计和实现。FPGA器件具有高度的灵活性和可编程性,可以根据不同的应用需求进行配置和重配置。FPGA片上可编程系统设计对于数字电路设计和实现具有重要的意义。

在FPGA器件中,时钟资源是非常重要的一部分。时钟资源是指FPGA器件中用于时序控制和同步的资源。时钟资源的设计和实现对FPGA器件的性能和可靠性具有重要的影响。

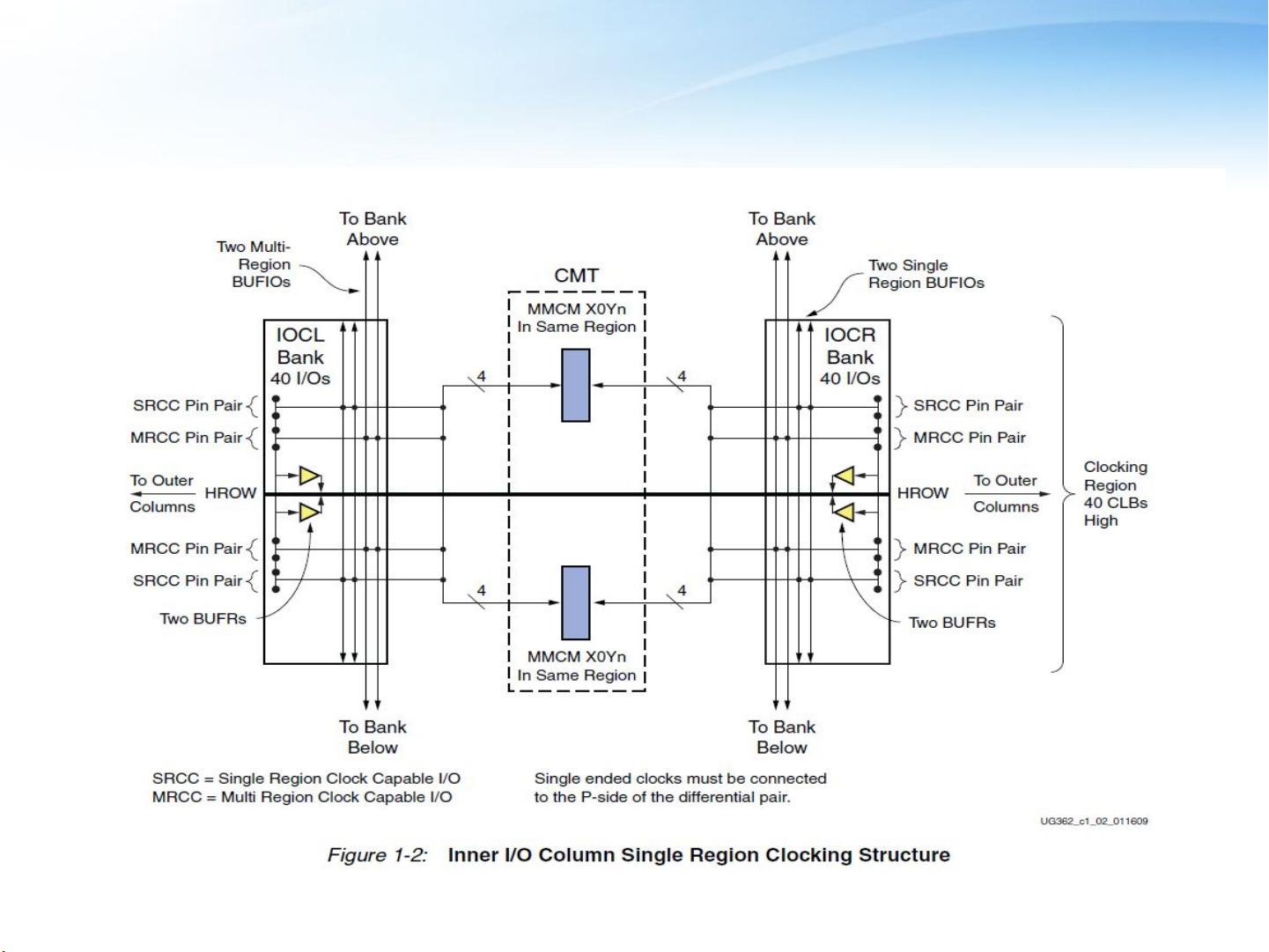

FPGA器件中的时钟资源可以分为两类:全局时钟资源和局域时钟资源。全局时钟资源是指FPGA器件中用于整个芯片的时序控制和同步的资源。局域时钟资源是指FPGA器件中用于局部区域的时序控制和同步的资源。

全局时钟资源包括全局时钟线和全局时钟缓冲器。全局时钟线是指FPGA器件中用于整个芯片的时序控制和同步的线路。全局时钟缓冲器是指FPGA器件中用于驱动全局时钟线的缓冲器。全局时钟缓冲器可以消除时钟分布延时,并调整与其它时钟的延时关系。

局域时钟资源包括局域时钟树和局域时钟驱动器。局域时钟树是指FPGA器件中用于局部区域的时序控制和同步的树形结构。局域时钟驱动器是指FPGA器件中用于驱动局域时钟树的驱动器。

在FPGA器件中,时钟管理块(CMT)是指FPGA器件中用于时钟管理和控制的模块。时钟管理块包括两个混合模式时钟管理器(MMCM),可以实现时钟的生成、分配和控制。

FPGA器件中的时钟资源设计和实现需要考虑多种因素,包括时钟频率、时钟相位、时钟延时、时钟抖动等。同时,FPGA器件中的时钟资源也需要与其他资源,如逻辑单元、存储单元、输入/输出单元等进行协调和互操作。

FPGA片上可编程系统设计中的时钟资源是非常重要的一部分,对FPGA器件的性能和可靠性具有重要的影响。因此,在FPGA器件设计和实现中,时钟资源的设计和实现需要受到充分的关注和考虑。

2021-07-13 上传

2021-07-13 上传

2023-12-26 上传

2023-07-27 上传

2023-11-18 上传

2023-04-20 上传

2023-08-08 上传

2023-05-12 上传

2023-04-28 上传

勇猛小丸子

- 粉丝: 3

- 资源: 14

最新资源

- WPF渲染层字符绘制原理探究及源代码解析

- 海康精简版监控软件:iVMS4200Lite版发布

- 自动化脚本在lspci-TV的应用介绍

- Chrome 81版本稳定版及匹配的chromedriver下载

- 深入解析Python推荐引擎与自然语言处理

- MATLAB数学建模算法程序包及案例数据

- Springboot人力资源管理系统:设计与功能

- STM32F4系列微控制器开发全面参考指南

- Python实现人脸识别的机器学习流程

- 基于STM32F103C8T6的HLW8032电量采集与解析方案

- Node.js高效MySQL驱动程序:mysqljs/mysql特性和配置

- 基于Python和大数据技术的电影推荐系统设计与实现

- 为ripro主题添加Live2D看板娘的后端资源教程

- 2022版PowerToys Everything插件升级,稳定运行无报错

- Map简易斗地主游戏实现方法介绍

- SJTU ICS Lab6 实验报告解析