优化ARM嵌入式系统:CPLD驱动的高效CF卡存储解决方案

160 浏览量

更新于2024-08-31

收藏 245KB PDF 举报

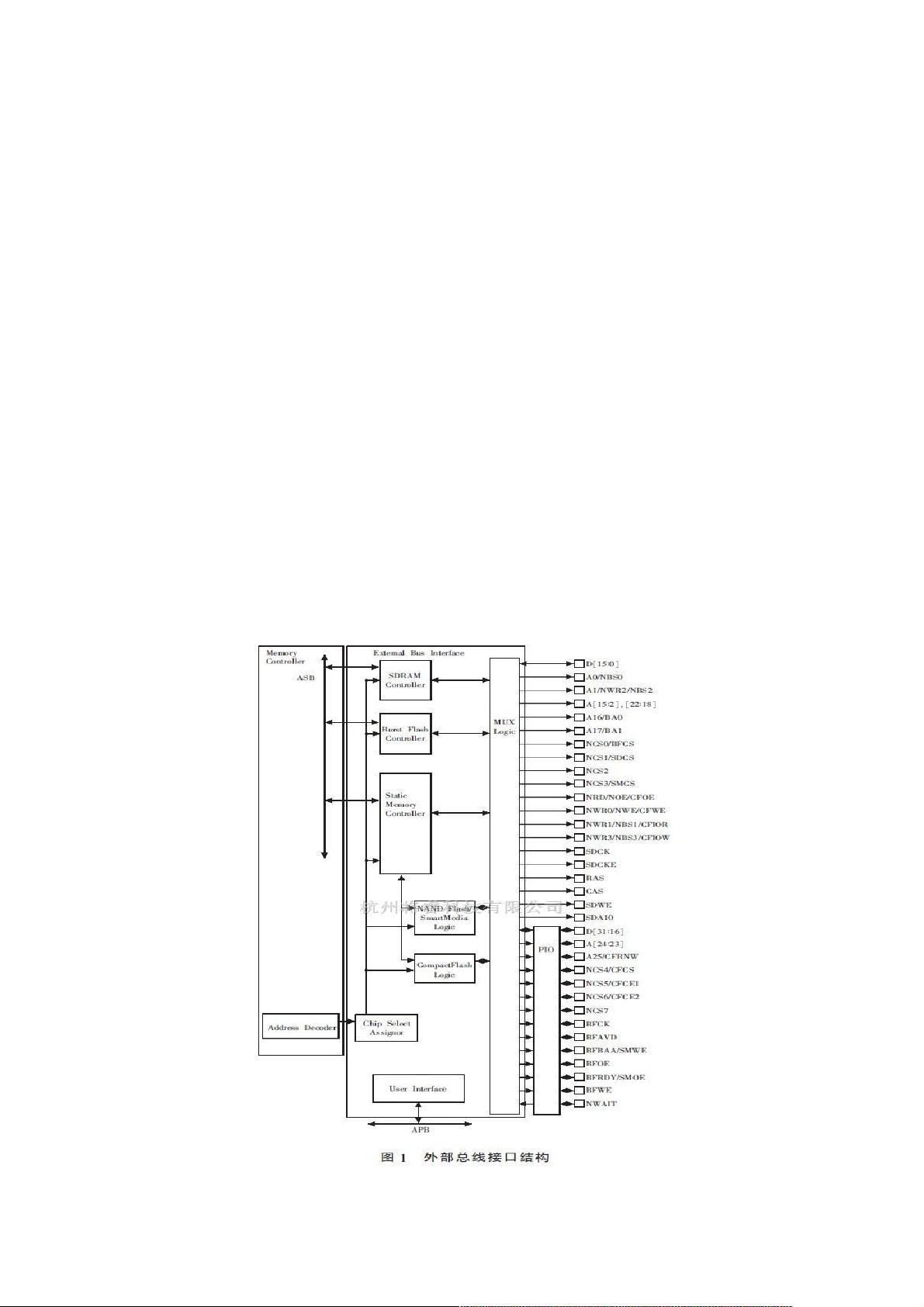

嵌入式系统/ARM技术中的基于ARM的嵌入式系统CF卡存储技术是一种针对现有CF卡接口存在的问题进行优化的设计方案。当前的CF卡接口电路普遍存在着接口复杂、稳定性不足以及存储速度慢等问题,这限制了其在嵌入式系统中的广泛应用。为了改善这些缺点,研究者深入分析了ARM处理器AT91RM9200的外部总线接口(EBI)以及CF卡和CPLD(复杂可编程逻辑器件)的工作原理。

新设计的CF卡接口电路采用了CPLD作为核心组件,取代了传统接口中的双向缓冲器、与非门等单一逻辑器件。CPLD的灵活性使得能够通过现场编程实现不同的逻辑功能,从而简化了电路结构,提高了系统的稳定性和存储速度。CPLD的使用使得电路设计更为高效,能够适应不断增长的应用需求。

实验结果表明,新设计的接口电路具有显著的优势,不仅在性能上有所提升,而且在易用性和可靠性方面也得到了增强,对于嵌入式系统中CF卡的高效存储提供了重要的参考价值。在现代嵌入式系统设计中,总线接口技术、特别是像EBI这样的高速接口,扮演了关键角色,因为它能够有效整合片内外存储资源,提升整体系统的效率。

关键词:嵌入式系统、ARM处理器、外部总线接口(EBI)、CF卡存储、CPLD编程和高速存储,这些都是设计和实现新型CF卡接口电路的关键要素。这项研究为解决嵌入式系统中的存储瓶颈问题提供了一种创新且实用的方法,推动了该领域的技术进步。

2008-12-25 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-12-05 上传

weixin_38558660

- 粉丝: 2

- 资源: 937

最新资源

- 李兴华Java基础教程:从入门到精通

- U盘与硬盘启动安装教程:从菜鸟到专家

- C++面试宝典:动态内存管理与继承解析

- C++ STL源码深度解析:专家级剖析与关键技术

- C/C++调用DOS命令实战指南

- 神经网络补偿的多传感器航迹融合技术

- GIS中的大地坐标系与椭球体解析

- 海思Hi3515 H.264编解码处理器用户手册

- Oracle基础练习题与解答

- 谷歌地球3D建筑筛选新流程详解

- CFO与CIO携手:数据管理与企业增值的战略

- Eclipse IDE基础教程:从入门到精通

- Shell脚本专家宝典:全面学习与资源指南

- Tomcat安装指南:附带JDK配置步骤

- NA3003A电子水准仪数据格式解析与转换研究

- 自动化专业英语词汇精华:必备术语集锦