Xilinx System Generator的以太网硬件协仿真:提升FPGA设计效率与带宽

104 浏览量

更新于2024-08-30

收藏 204KB PDF 举报

在电子设计自动化(EDA)和可编程逻辑器件(PLD)的设计过程中,传统的基于FPGA的大型信号处理系统设计往往面临着繁琐和低效的仿真挑战。为了提升效率并优化开发流程,Xilinx的System Generator for DSP这类工具引入了硬件在环(Hardware-in-the-Loop, HIL)技术,特别是通过以太网硬件协仿真接口。

硬件在环接口的核心价值在于它可以直接将FPGA硬件模块整合到设计仿真环境中,从而加速仿真过程。相较于传统软件仿真,硬件在环能够提供几个数量级的性能提升,显著节省设计人员的时间,并且允许实时硬件调试和验证,这对于复杂系统的早期阶段测试和优化至关重要。

System Generator for DSP支持多种FPGA开发平台,通过不同物理接口如JTAG或PCI与个人计算机进行通信。例如,JTAG接口适用于配备JTAG头和Xilinx FPGA的板卡,而像XtremeDSP这样的套件则依赖于PCI总线。然而,对于那些对存储带宽和吞吐率需求较高的系统,例如视频和图像处理应用,以往的限制在于必须使用PCI或PCMCIA接口连接到PC。

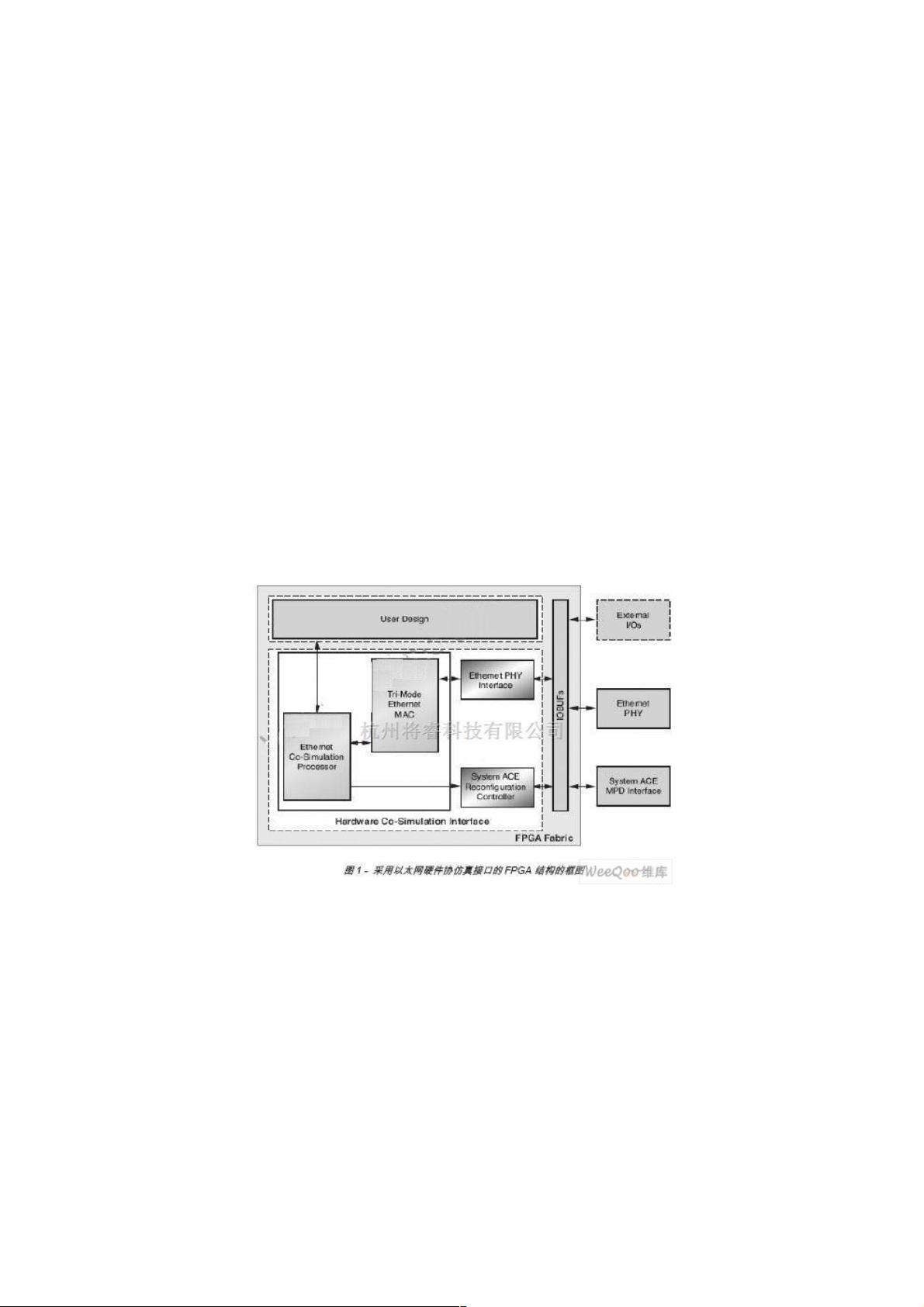

System Generator for DSP 8.1版本的一个重大革新是引入了以太网协仿真接口。这个接口首次使得Xilinx ML402等开发平台能够实现高速、高带宽的协仿真,可以直接通过标准以太网连接到本地计算机,或者通过网络远程接入。接口的核心是Xilinx的三态以太网MAC核,它支持10/100/1000Mbps的半双工和全双工通信模式,这极大地扩展了FPGA设计的仿真能力,特别是在需要大量数据传输的应用场景下。

总结来说,利用以太网硬件协仿真接口在EDA/PLD设计中实现了高效和便捷的仿真体验,不仅提高了仿真速度,还支持实时硬件调试,对于FPGA开发平台的兼容性和带宽优化具有重要意义。这一创新为设计师提供了更灵活和强大的工具,推动了现代信号处理系统设计的迭代和发展。

111 浏览量

151 浏览量

104 浏览量

2024-11-04 上传

2024-10-27 上传

2024-11-02 上传

2024-11-02 上传

2024-10-31 上传

2024-11-11 上传