FPGA/CPLD数字电路设计:时序优化与经验探讨

需积分: 3 18 浏览量

更新于2024-08-02

收藏 930KB PDF 举报

"FPGA/CPLD设计经验分享,涵盖了数字电路设计中的时序设计、建立时间、保持时间等关键概念。"

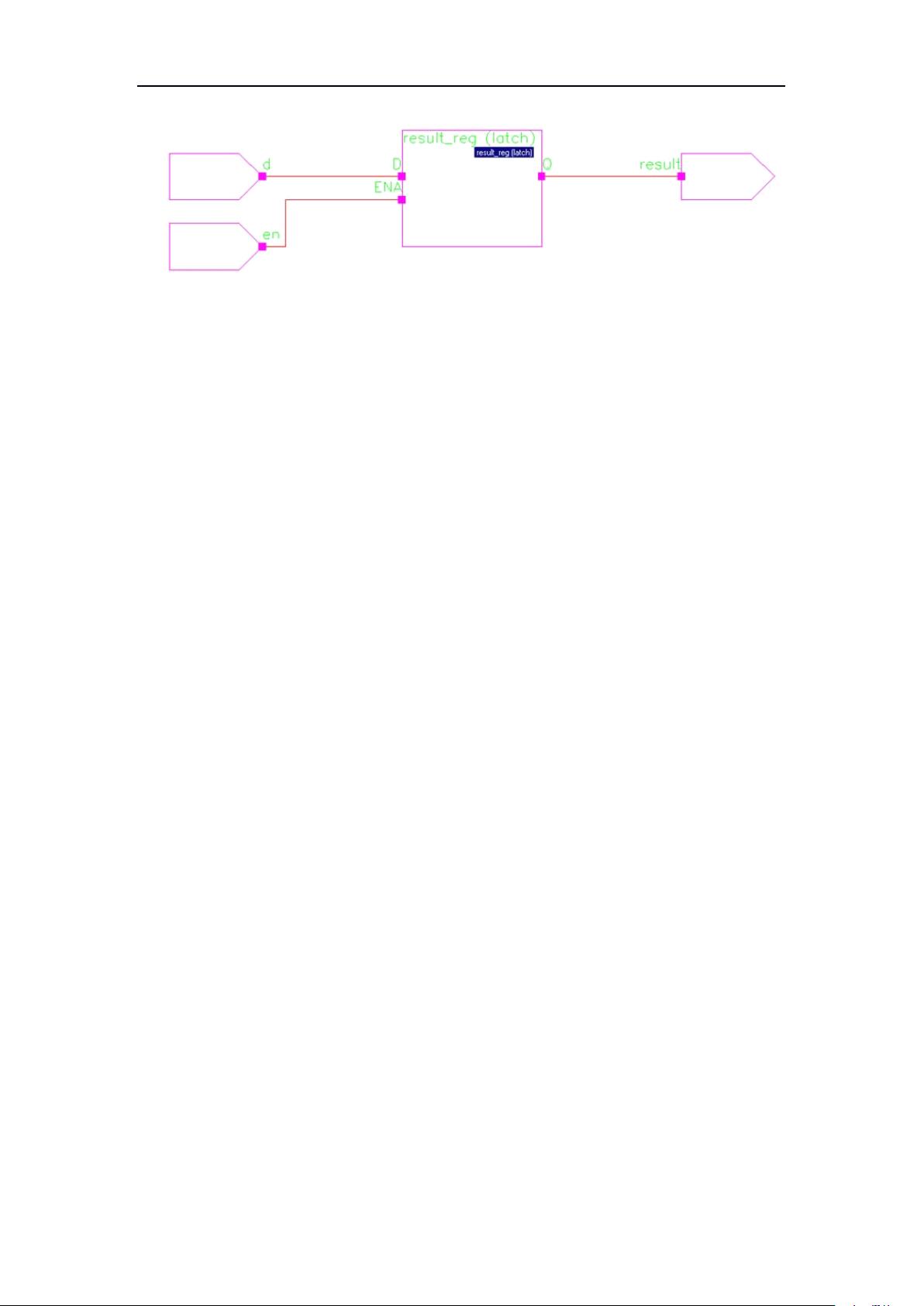

在FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)设计中,理解和掌握数字电路的时序设计至关重要。时序设计是衡量系统性能的重要指标,尤其是在使用高层次设计方法时,由于抽象度增加,时序控制的难度也随之提升。然而,通过对RTL(Register Transfer Level)电路的时序模型的理解,采用合理的设计方法,可以有效地应对这一挑战。

首先,要明确数字电路设计中的两个基本概念:建立时间和保持时间。建立时间(setup time)是指数据必须在触发器时钟上升沿到来之前保持稳定的时间,以确保数据能够正确地被捕捉到触发器。如果数据在时钟上升沿到达前未稳定,就会导致错误。另一方面,保持时间(hold time)是指时钟上升沿之后数据需要保持不变的时间,以确保数据在触发器内部处理过程中不会发生变化。这两个参数对于确保数字系统的正确运行至关重要。

在实际设计中,考虑到时钟树的偏斜,建立时间的约束与时钟周期紧密相关。如果系统在高频时钟下无法正常工作,降低时钟频率通常可以解决问题。相比之下,保持时间并不依赖于时钟周期,而是更多地受到布局布线的影响。一旦设计中保持时间不足,即使调整时钟频率也无法解决,可能需要对整个设计进行大幅度修改,这无疑降低了设计效率。

在FPGA/CPLD的设计中,由于可编程逻辑器件的特性,时钟树的偏斜通常可以忽略,因此保持时间问题相对较少。但建立时间仍然是设计者需要关注的重点。通过软件工具,如FPGA/CPLD开发软件,可以自动计算输入信号的建立和保持时间,帮助设计师优化设计,确保仿真通过率,并实现较高的工作频率。

要成功地进行FPGA/CPLD设计,设计师必须深入理解并熟练应用时序设计原则,包括建立时间和保持时间的管理。通过有效的设计策略和工具支持,可以显著提高设计的成功率和系统性能。同时,分享此类设计经验对于新手和资深工程师来说都是宝贵的学习资源,有助于整个行业的知识传承和技能提升。

2010-05-19 上传

2009-03-14 上传

2008-10-24 上传

2023-05-12 上传

2023-06-14 上传

2023-05-11 上传

2023-07-17 上传

2023-06-28 上传

2023-08-08 上传

save2006

- 粉丝: 0

- 资源: 3

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍