华为静态时序分析与逻辑设计详解

需积分: 33 188 浏览量

更新于2024-07-25

收藏 598KB PDF 举报

"华为静态时序分析与逻辑设计"

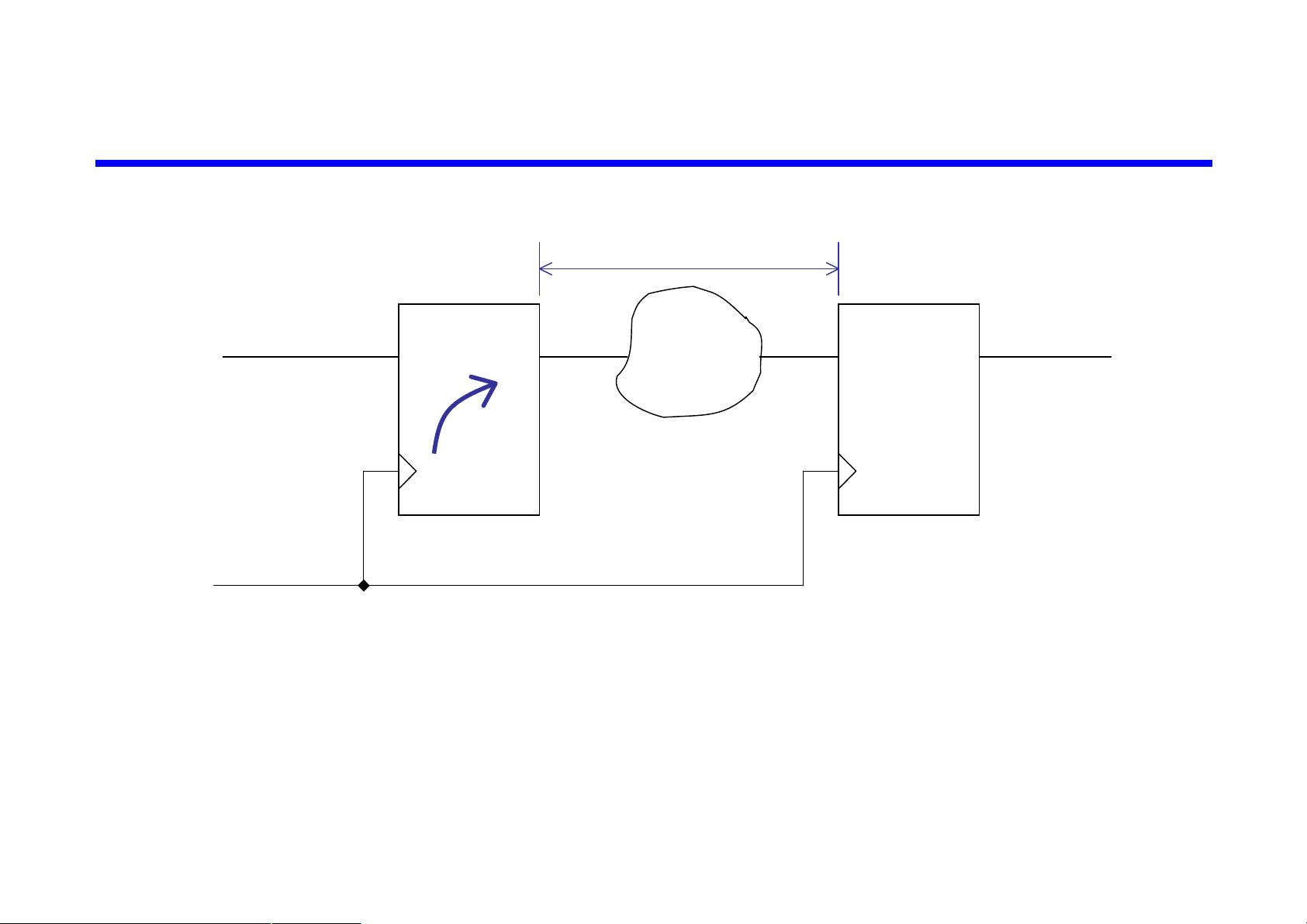

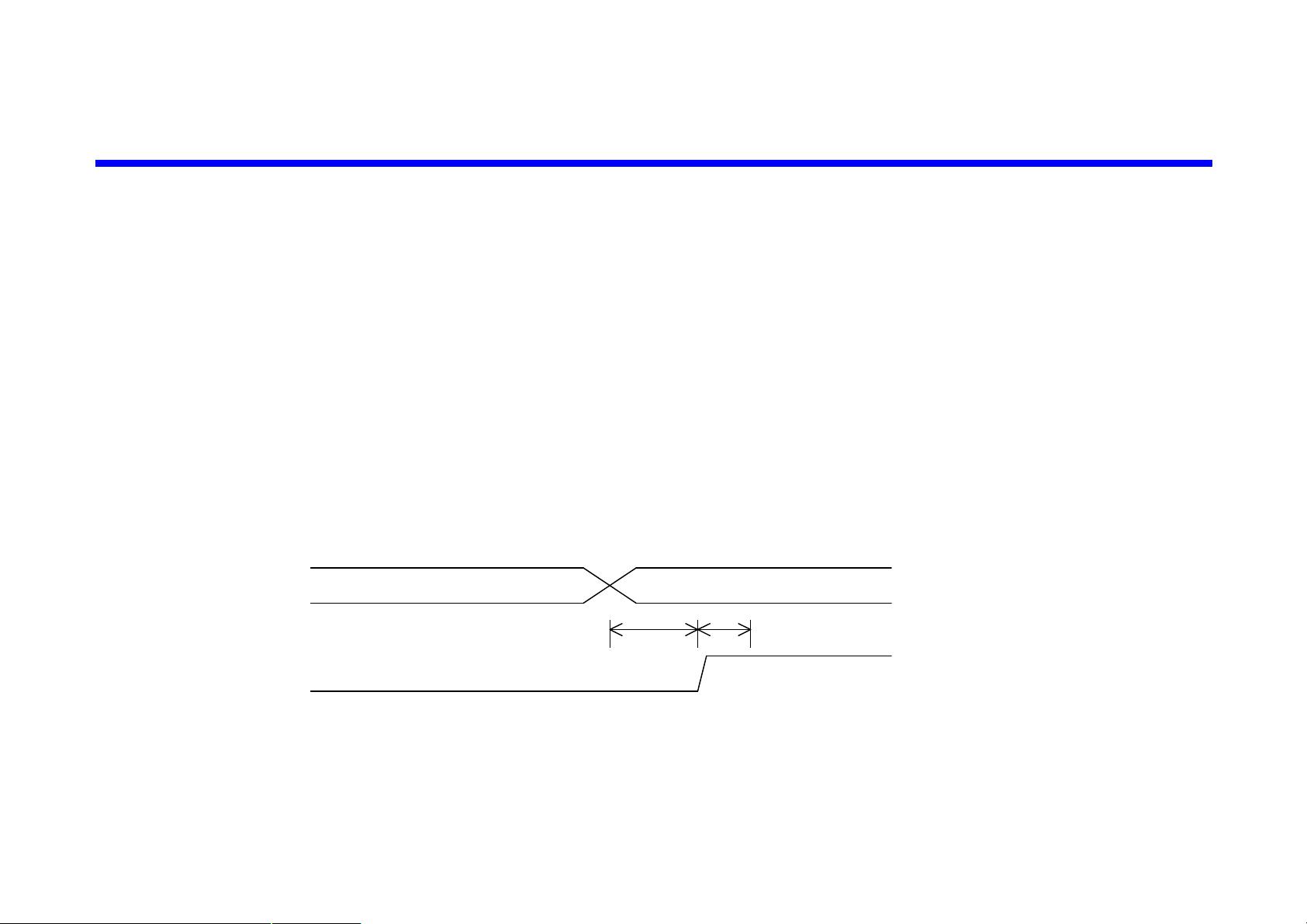

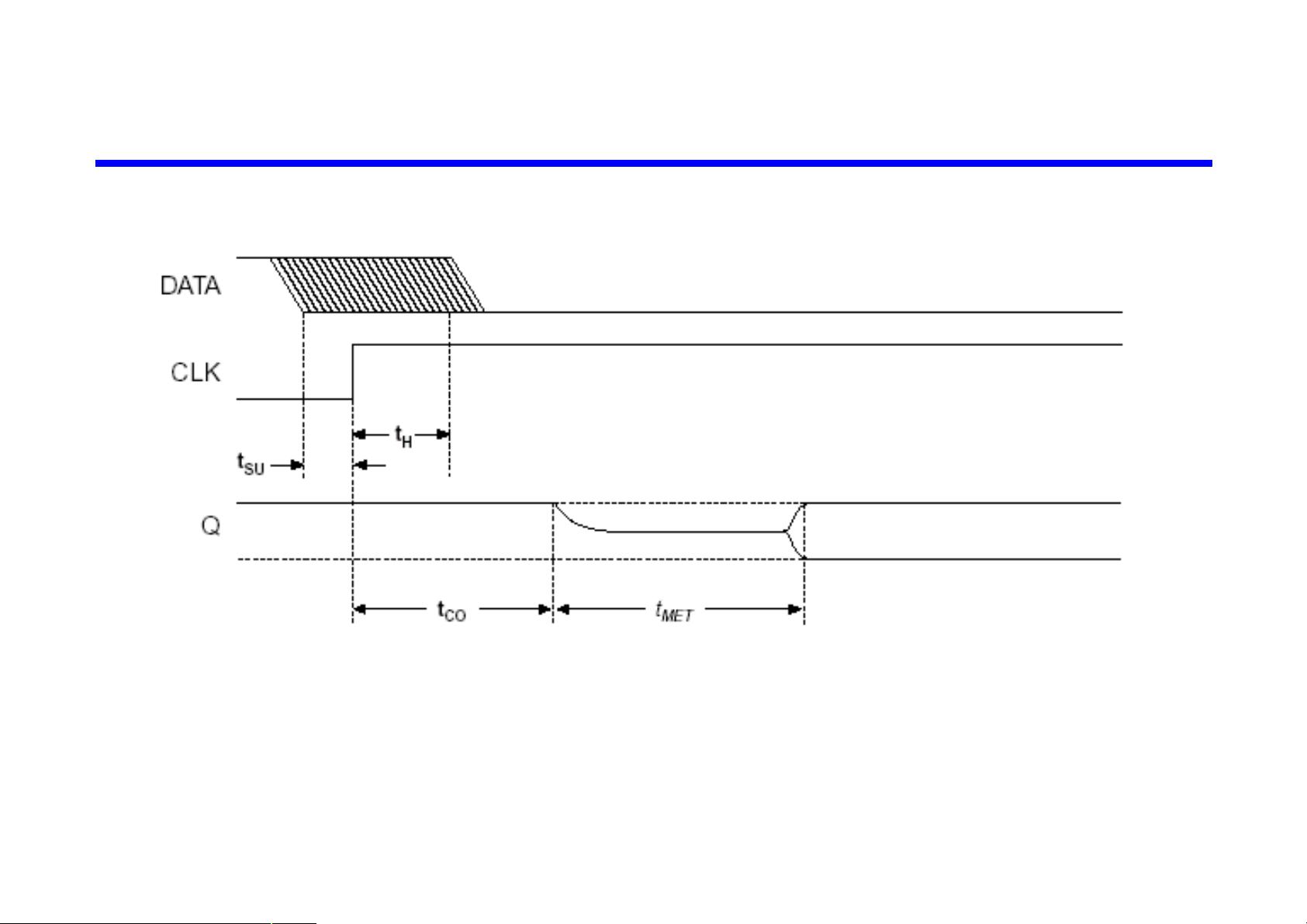

这篇资料详细介绍了华为在静态时序分析(Static Timing Analysis,简称STA)方面的应用和技术。静态时序分析是集成电路设计中的关键步骤,用于验证数字电路设计是否满足预定的时序要求,确保在各种工艺、电压和温度条件下的正确工作。

首先,文档提及了BTS,这可能是某种特定的工具或流程,它可能包含了2003年第四版的Version1.0。文档中包含了各种命令和格式,如"",这些可能表示特定的工具指令或者数据结构,用于进行时序分析。

接着,文档提到了“TimingAnalyzer”,这是一个常见的时序分析工具,用于分析电路中的路径延迟并确定是否存在时序违规。它能帮助工程师识别电路中最慢的路径,以便优化设计。

文档还涉及到了“StaticTimingAnalysis(STA)”的讨论,这是静态时序分析的核心概念,通过分析门级网表,计算每个时钟周期内的最大和最小延迟,从而评估设计的时序性能。STA能够提供精确的时序信息,而无需实际运行电路。

文中提到了Synopsys的PrimeTime和MentorGraphics的SSTVelocity,以及Innoveda的Blast89和FPGA相关工具,这些都是业界知名的静态时序分析软件,广泛应用于IC设计和FPGA开发。它们能够帮助工程师进行时序收敛(timing closure),确保设计满足速度等级和电源电压的要求。

此外,文档还涉及到ASIC(Application-Specific Integrated Circuit)和FPGA(Field-Programmable Gate Array)的设计,这两者都是集成电路的不同类型。ASIC是为特定应用定制的芯片,而FPGA是可编程逻辑器件,可以在使用前进行配置。

最后,文档中的一些专业术语如“"100%"、"¥¦§

¦¨©ª¥"等可能是错误的字符编码或者是特定工具的内部代码,需要结合具体的上下文来解读。

这份资料涵盖了静态时序分析的重要概念、工具和应用场景,对理解和实践华为的逻辑设计过程具有重要的参考价值。

2011-01-24 上传

2009-03-02 上传

点击了解资源详情

点击了解资源详情

2021-09-10 上传

2010-05-13 上传

2021-10-15 上传

2021-10-10 上传

2018-03-15 上传

wsmsn

- 粉丝: 0

- 资源: 3