FPGA实现简易电子密码锁设计与代码解析

版权申诉

14 浏览量

更新于2024-06-26

收藏 9.86MB DOCX 举报

"该文档提供了一款基于FPGA实现的简易电子密码锁的设计说明和代码资料,旨在通过FPGA控制直流电机实现锁的开关,并具备密码输入、超时复位和报警功能。设计中使用了VHDL语言,主要包括顶层文件time.bdf和其他子模块。硬件部分包括数码管、按键、蜂鸣器、LED、FPGA、电源、晶振等组件。"

本文档详细介绍了基于FPGA的简易电子密码锁设计,主要知识点包括:

1. **FPGA开发**:FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,允许用户根据需求定制数字逻辑电路。在这个项目中,FPGA被用来实现密码锁的逻辑控制,包括密码验证、时间计数和电机控制等功能。

2. **密码验证逻辑**:设计要求密码长度为4位,且可以修改。用户需要在5秒内输入4个数字,如果输入的密码与存储的密码匹配,将输出开锁信号。不匹配或超时则会触发自锁和报警。

3. **VHDL编程**:VHDL是硬件描述语言,用于描述数字系统的结构和行为。在这个项目中,VHDL被用来编写密码锁的逻辑控制代码,包括顶层文件time.bdf和其他子模块。

4. **硬件接口**:

- **数码管**:用于显示密码输入的状态和当前密码,左侧数码管指示当前输入的密码位数,右侧数码管显示实际输入的密码。

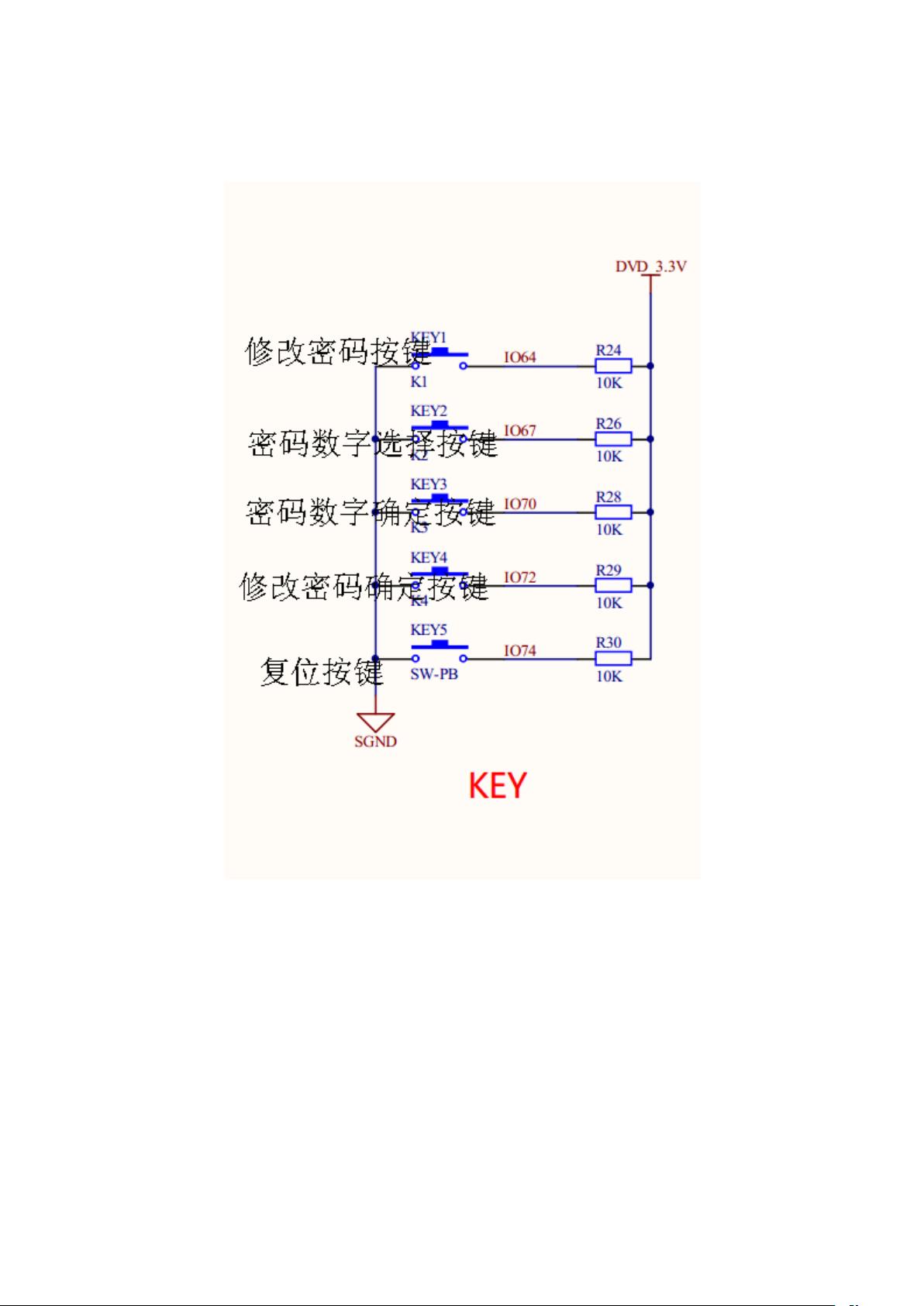

- **按键**:Key2用于选择密码数字,Key3用于确认输入,此外可能还有复位键用于系统复位。

- **蜂鸣器**:在超时或错误输入时发出报警信号。

- **LED**:红绿灯分别表示锁的状态,红灯亮表示锁闭,绿灯亮表示开启。

- **电源、晶振**:为整个系统提供稳定的工作电压和时钟信号。

5. **系统操作流程**:

- **上电**:连接5V电源,数码管显示"00000",系统初始化。

- **复位**:按下复位键,所有显示清零,电子锁进入自锁状态。

- **密码输入**:通过Key2选择数字,Key3确认输入,每输入一位密码,左侧数码管递增,5秒内输入4位完成。

- **超时与报警**:如果5秒内未完成输入,系统自动复位并启动蜂鸣器报警20秒。

- **密码验证**:输入正确密码后,绿灯亮起,电机驱动执行机构解锁;输入错误则保持锁定状态。

6. **设计挑战**:确保在限制时间内完成密码输入,避免系统自锁;正确处理各种异常情况,如按键错误、超时等。

通过这个项目,学习者可以掌握FPGA的基础应用、VHDL编程技巧以及硬件接口设计,同时锻炼实际问题解决能力。

2022-06-22 上传

2023-04-26 上传

2023-04-26 上传

2023-04-26 上传

2023-07-03 上传

通信瓦工

- 粉丝: 374

- 资源: 6484