B3G MIMO-OFDM系统定时同步算法 FPGA实现与优化

需积分: 9 170 浏览量

更新于2024-08-11

收藏 382KB PDF 举报

"B3G MIMO-OFDM系统的定时同步算法实现 (2007年)"

正文:

本文深入探讨了在B3G (Beyond 3G) MIMO-OFDM系统中定时同步算法的实现策略,特别是针对如何降低截位操作对性能的影响以及简化算法实现的复杂度。定时同步在无线通信系统中起着至关重要的作用,因为它确保了正确的时间对齐,从而避免信号失真和数据解码错误。

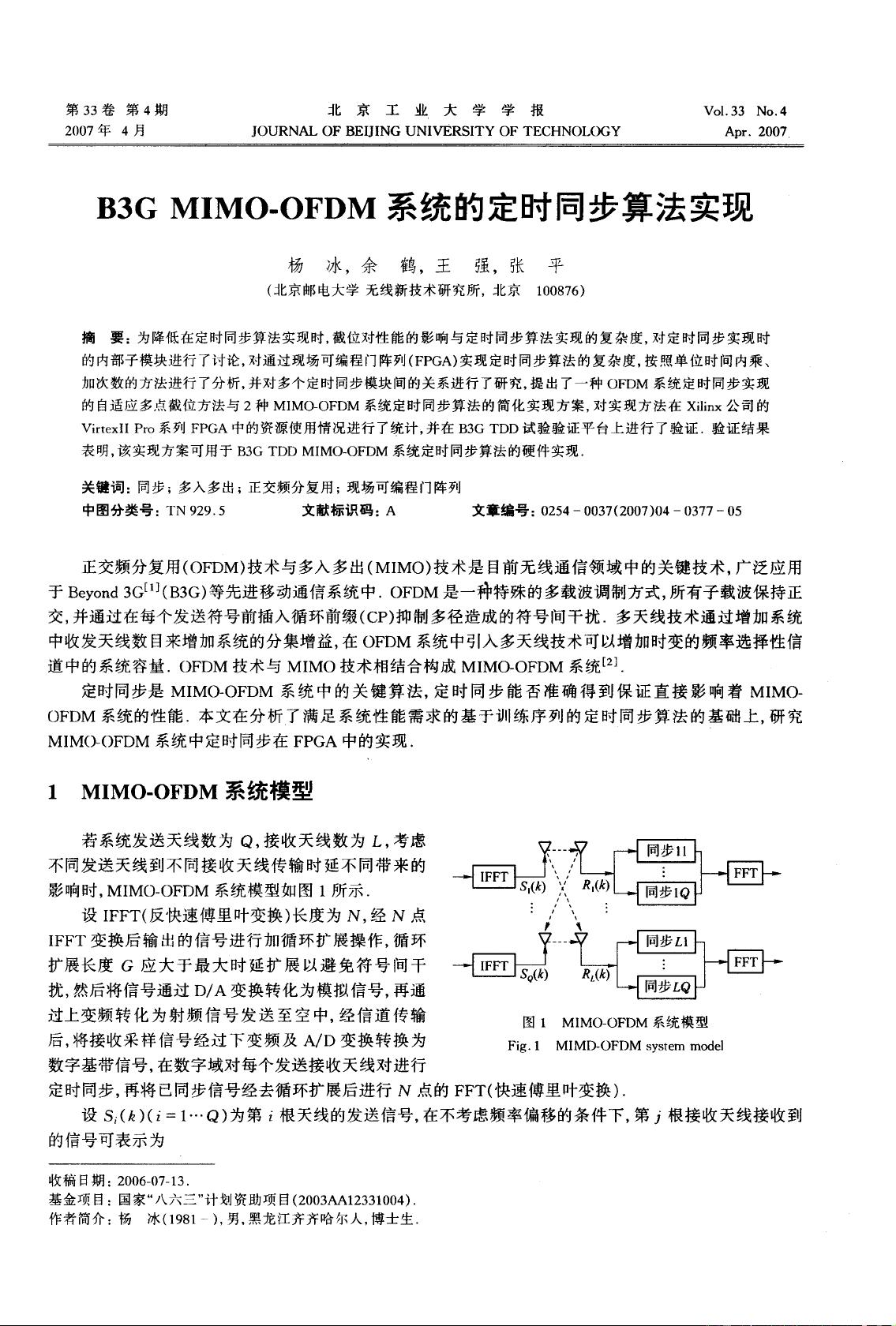

在MIMO-OFDM系统中,正交频分复用(OFDM)与多入多出(MIMO)技术结合,提供更高的数据传输速率和系统容量。OFDM利用多个子载波的正交性来减少多径传播引起的干扰,而MIMO技术通过增加发射和接收天线的数量来增强系统的空间分集和容量。然而,由于无线信道的时变特性,定时同步成为确保有效通信的关键。

论文首先分析了基于训练序列的定时同步算法,这些算法依赖于系统内的已知参考信号来估计和调整接收机的定时。作者讨论了在实现这些算法时内部子模块的功能,特别是在现场可编程门阵列(FPGA)上的实现复杂度。FPGA是一种可编程芯片,常用于实现高速、低延迟的数字逻辑功能,如定时同步。

为了减少FPGA实现定时同步的计算负担,文章提出了自适应多点截位方法。这种方法能够根据信号质量动态调整截位点,既保证了性能,又降低了计算复杂度。此外,作者还提出了两种MIMO-OFDM系统的定时同步算法的简化实现方案,这些方案旨在减少硬件资源的使用,同时保持所需性能水平。

在Xilinx公司的VirtexII Pro系列FPGA上,这些实现方法被进行资源占用分析,并在B3G TDD (时分双工)实验验证平台上进行了实际测试。实验结果证实了这些方法的有效性,适合于B3G TDD MIMO-OFDM系统的硬件实现。

这篇论文提供了关于B3G MIMO-OFDM系统定时同步算法实现的深入洞察,包括算法设计、复杂度分析、FPGA实现以及实际性能验证。这些研究成果对于优化MIMO-OFDM系统的实时性能,特别是在资源有限的硬件平台上具有重要的理论和实践价值。

2020-08-13 上传

2009-12-14 上传

2010-10-10 上传

2023-05-09 上传

2023-05-15 上传

2023-05-15 上传

2023-05-01 上传

2023-05-12 上传

2023-11-08 上传

weixin_38686924

- 粉丝: 14

- 资源: 956

最新资源

- 深入浅出:自定义 Grunt 任务的实践指南

- 网络物理突变工具的多点路径规划实现与分析

- multifeed: 实现多作者间的超核心共享与同步技术

- C++商品交易系统实习项目详细要求

- macOS系统Python模块whl包安装教程

- 掌握fullstackJS:构建React框架与快速开发应用

- React-Purify: 实现React组件纯净方法的工具介绍

- deck.js:构建现代HTML演示的JavaScript库

- nunn:现代C++17实现的机器学习库开源项目

- Python安装包 Acquisition-4.12-cp35-cp35m-win_amd64.whl.zip 使用说明

- Amaranthus-tuberculatus基因组分析脚本集

- Ubuntu 12.04下Realtek RTL8821AE驱动的向后移植指南

- 掌握Jest环境下的最新jsdom功能

- CAGI Toolkit:开源Asterisk PBX的AGI应用开发

- MyDropDemo: 体验QGraphicsView的拖放功能

- 远程FPGA平台上的Quartus II17.1 LCD色块闪烁现象解析