DDR内存详解与DDR2技术规范

需积分: 14 117 浏览量

更新于2024-07-26

1

收藏 2.97MB DOCX 举报

"DDRPCB设计要求规范,讲解了DDR2和DDR3内存的原理与特性,以及PCB布线注意事项"

DDR(Double Data Rate)内存技术是SDRAM的一个升级版本,其核心特点在于在一个时钟周期内传输两次数据,利用上升沿和下降沿,从而显著提高了数据传输速率。DDR2内存进一步提升了这一性能,通过4bit的数据预读取技术,使得数据处理能力翻倍。

DDR内存的工作原理:

DDR内存与传统的SDRAM不同,SDRAM在一个时钟周期内仅传输一次数据,而DDR则在每个时钟周期的上升沿和下降沿分别传输一次,因此其数据传输速率是SDRAM的两倍。DDR内存使用了DLL技术,确保数据的精确定位和同步,提升了系统性能。

DDR2内存的改进:

DDR2内存作为DDR的下一代产品,主要改进在于预读取机制。DDR2内存将预读取位宽从DDR的2bit提升到4bit,这意味着它可以在每个时钟周期内处理更多的数据。此外,DDR2内存还降低了工作电压,从DDR的2.5V降至1.8V或1.5V,这有助于减少功耗和发热量。

PCB布线注意事项:

设计DDR内存的PCB板时,有以下几点需要注意:

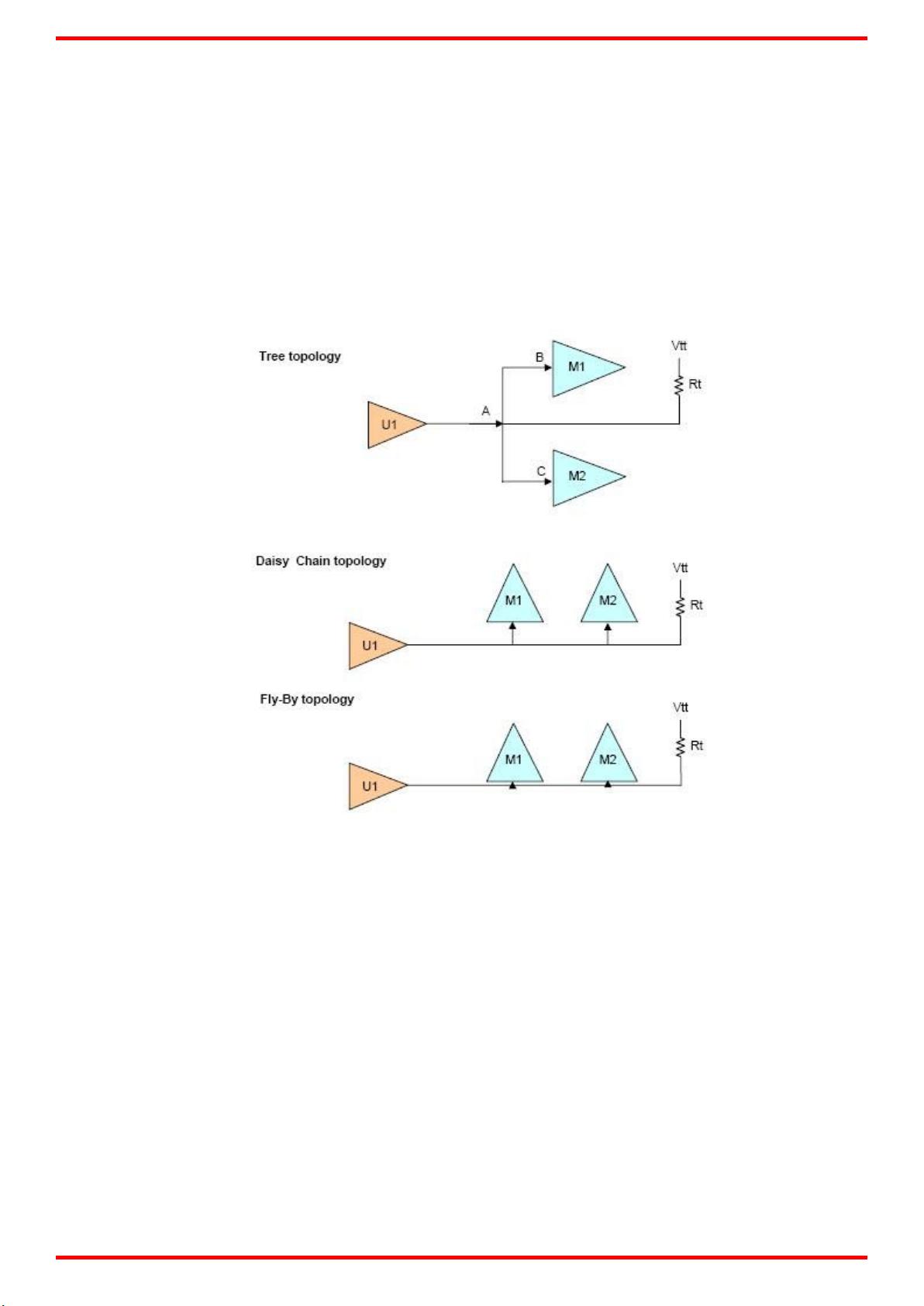

1. **信号完整性**:由于DDR内存的高速特性,信号完整性的保持至关重要。设计师应确保信号的上升时间、下降时间和延迟时间满足内存芯片的要求,避免信号失真和反射。

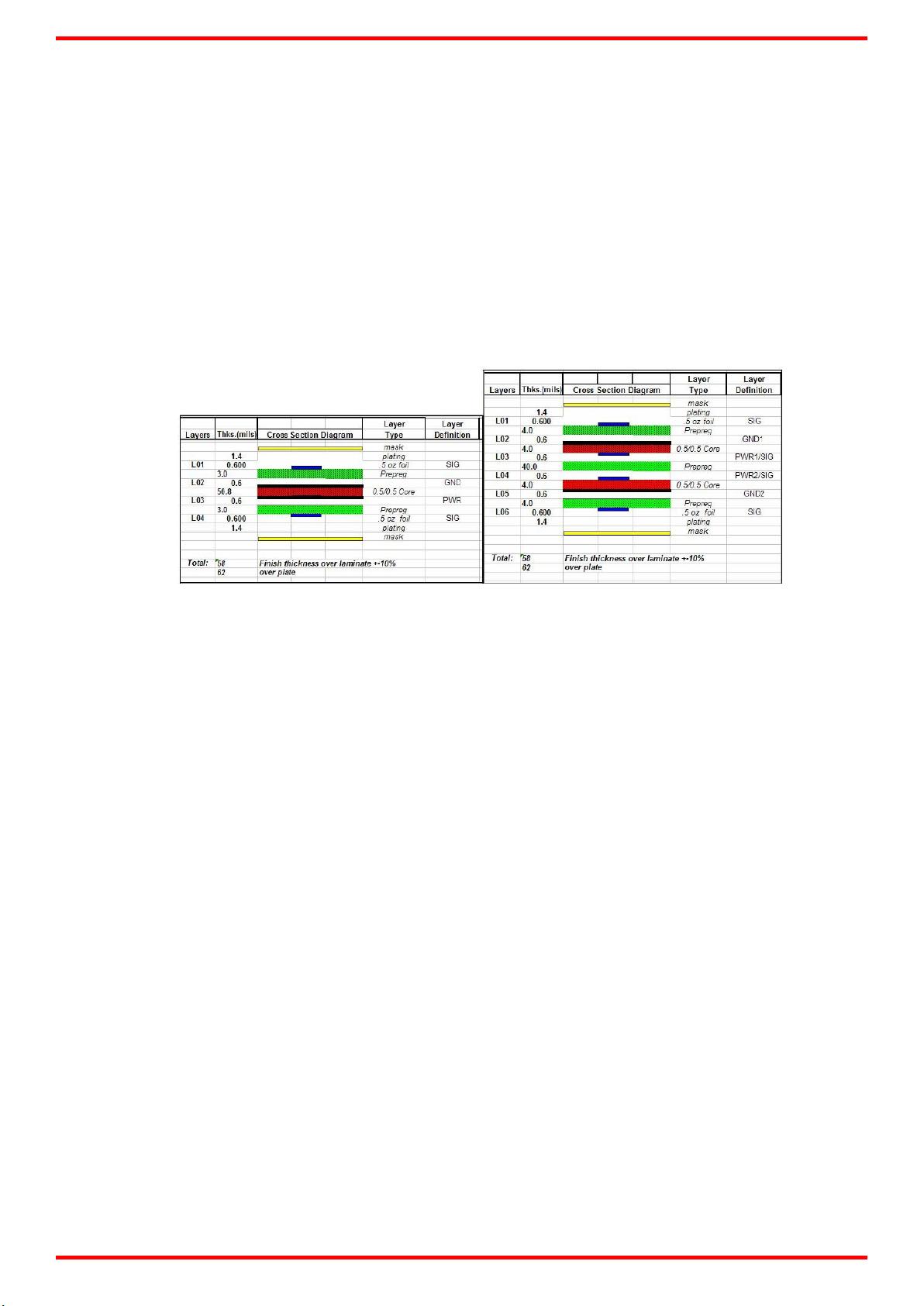

2. **阻抗匹配**:为了减少信号损失和反射,布线时需要考虑信号线的阻抗匹配。通常,DDR内存的走线需要保持50欧姆的特性阻抗。

3. **时钟对齐**:时钟信号的准确传输对DDR内存的性能至关重要。时钟线应尽可能短且直,与其他数据线保持一定的距离,以减少时钟信号的干扰。

4. **电源和地线规划**:良好的电源和地线布局可以减少噪声和电磁干扰。电源层和地层应尽可能靠近,形成紧密的电源-地平面结构,以提供低阻抗的返回路径。

5. **布线间距**:DDR内存的信号线之间应保持合适的间距,以防止串扰。根据DDR内存的规格,数据线和地址线之间的间距应符合制造商的建议。

6. **去耦电容**:在内存芯片附近放置适当的去耦电容,可以提供瞬态电流需求并滤除电源噪声。

7. **避免过孔**:减少DDR内存信号线上的过孔数量,因为过孔会引入额外的延迟和阻抗变化,影响信号质量。

8. **时序调整**:如果可能,应使用时序分析工具对DDR内存的时序进行优化,确保所有内存模块在同一时钟周期内同步。

9. **热设计**:考虑到DDR2内存的低电压和高密度,散热设计也是不可忽视的,需要确保内存工作在合适的温度范围内。

DDR2和DDR3内存的PCB设计需要综合考虑信号完整性、电源稳定性、时序约束等多个方面,以实现高效、可靠的系统运行。设计时应遵循内存制造商提供的设计指南,并使用专业的PCB设计软件进行仿真和优化。

357 浏览量

1123 浏览量

202 浏览量

103 浏览量

259 浏览量

372 浏览量

830 浏览量

138 浏览量

2020-08-03 上传

xsx1990xsx

- 粉丝: 0

- 资源: 8

最新资源

- 单片机模拟I2C总线及24C02(I2C EEPROM)读写实例.doc

- you can do it

- 用Matlab扩展Excel的功能.pdf

- 线性代数3版习题详细解答

- UML Reference Manual 英文版 (pdf)

- 一些不错的开源Flex项目.txt

- 解析Linux特殊文件

- Modelsim安装步骤

- Cactus 业务流程执行平台的研究和实现

- [美]P[1].德苏泽+J.pdf

- python--Python 学习笔记

- LCD驱动显示原理及驱动开发

- Apress+-+Expert+Shell+Scripting.pdf

- Ubuntu+Server+Administration+.pdf

- Manning[1].Hibernate.Search.In.Action.Dec.2008.pdf

- Flex 3 cookbook 简体中文(全)