SystemVerilog笔记:关键概念与语法解析

需积分: 0 120 浏览量

更新于2024-08-04

收藏 1.31MB DOCX 举报

"SystemVerilog学习笔记,包括关键词rand、randc、约束constraint、伪随机数生成器PRNG、数据类型、数组、结构体、过程块和方法等内容,适合初学者入门学习。"

SystemVerilog是一种高级的硬件描述语言,广泛用于集成电路验证。这篇笔记主要涵盖了几个关键知识点,帮助初学者理解和掌握SystemVerilog的基础。

1. 随机化(Randomization)

SystemVerilog中的`rand`关键字允许声明随机变量,`randc`则引入周期性的随机性,确保所有可能的值都被遍历后再重复。这些变量需要与`std::randomize()`函数配合使用,以生成随机数。`local::`是限制随机化作用域的关键词,只在`randomize`内部有效。伪随机数生成器(PRNG)通过特定算法产生看似随机但实际上确定的数列。

2. 约束(Constraints)

`constraint`用于定义随机化变量的约束条件。`inside{}`用于指定变量可以取的值的范围,`dist`用于定义权重分布。例如,`dist = {[$:4]}`表示均匀分布,而`:/:`可以用来平均分配权重。箭头`->`用于条件约束,如果前一个表达式为真,就会执行后面的约束。

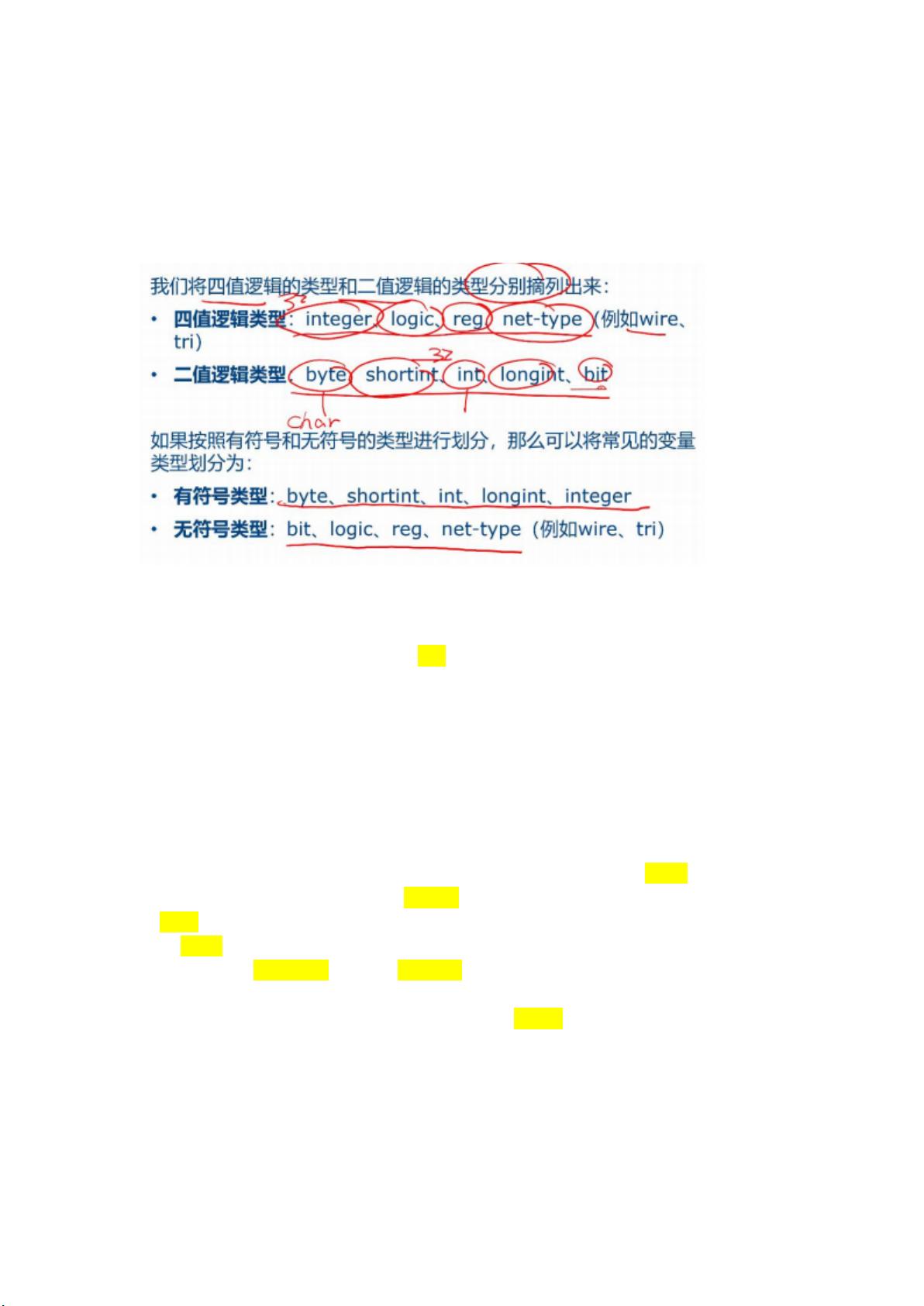

3. 数据类型

- `logic`类型是SystemVerilog中的通用类型,它可以表示任何逻辑值,包括未知值。

- 数字类型有二进制`b`, 八进制`o`, 十进制`d`和十六进制`h`。

4. 数组类型

- 定宽数组:宽度在声明时确定,不可改变。

- 动态数组:在仿真时分配空间,宽度可变。

- 关联数组:用于稀疏矩阵,仅存储实际写入的元素,节省空间。

- 合并数组:可以作为单独数据或数组使用,格式为`[msb:lsb]`。

- 队列:结合了链表和数组的特性,支持高效插入和删除,以及通过索引访问。

5. 新的数据类型创建

- `typedef`用于创建新的数据类型,如结构体`struct`,但SystemVerilog的结构体功能有限。

- 枚举类型`enum`可以定义用户自定义的枚举类型,方便共享。

- `string`类型用于处理文本字符串,`$sformatf()`和`$display()`用于格式化输出和显示。

6. 过程块和方法

- 硬件描述:`module`和`interface`代表硬件行为,而`program`和`class`用于软件风格的编程。

- `always`块用于描述硬件行为,平行执行,`initial`块只执行一次,不支持延迟。

- `always_comb`、`always_latch`和`always_ff`分别用于组合逻辑、保持和时序逻辑描述。

这些笔记内容覆盖了SystemVerilog的基础概念和常用语法,是初学者系统学习SystemVerilog的重要参考资料。通过深入理解和实践这些知识点,可以更好地进行IC验证工作。

2022-10-26 上传

1395 浏览量

2022-05-09 上传

2023-07-12 上传

2023-06-08 上传

点击了解资源详情

点击了解资源详情

2023-06-24 上传

验证小猴子

- 粉丝: 1

- 资源: 1

最新资源

- Java集合ArrayList实现字符串管理及效果展示

- 实现2D3D相机拾取射线的关键技术

- LiveLy-公寓管理门户:创新体验与技术实现

- 易语言打造的快捷禁止程序运行小工具

- Microgateway核心:实现配置和插件的主端口转发

- 掌握Java基本操作:增删查改入门代码详解

- Apache Tomcat 7.0.109 Windows版下载指南

- Qt实现文件系统浏览器界面设计与功能开发

- ReactJS新手实验:搭建与运行教程

- 探索生成艺术:几个月创意Processing实验

- Django框架下Cisco IOx平台实战开发案例源码解析

- 在Linux环境下配置Java版VTK开发环境

- 29街网上城市公司网站系统v1.0:企业建站全面解决方案

- WordPress CMB2插件的Suggest字段类型使用教程

- TCP协议实现的Java桌面聊天客户端应用

- ANR-WatchDog: 检测Android应用无响应并报告异常

已收录资源合集

已收录资源合集