Cadence Allegro SI 16.3:高速电路中的信号完整性仿真关键解析

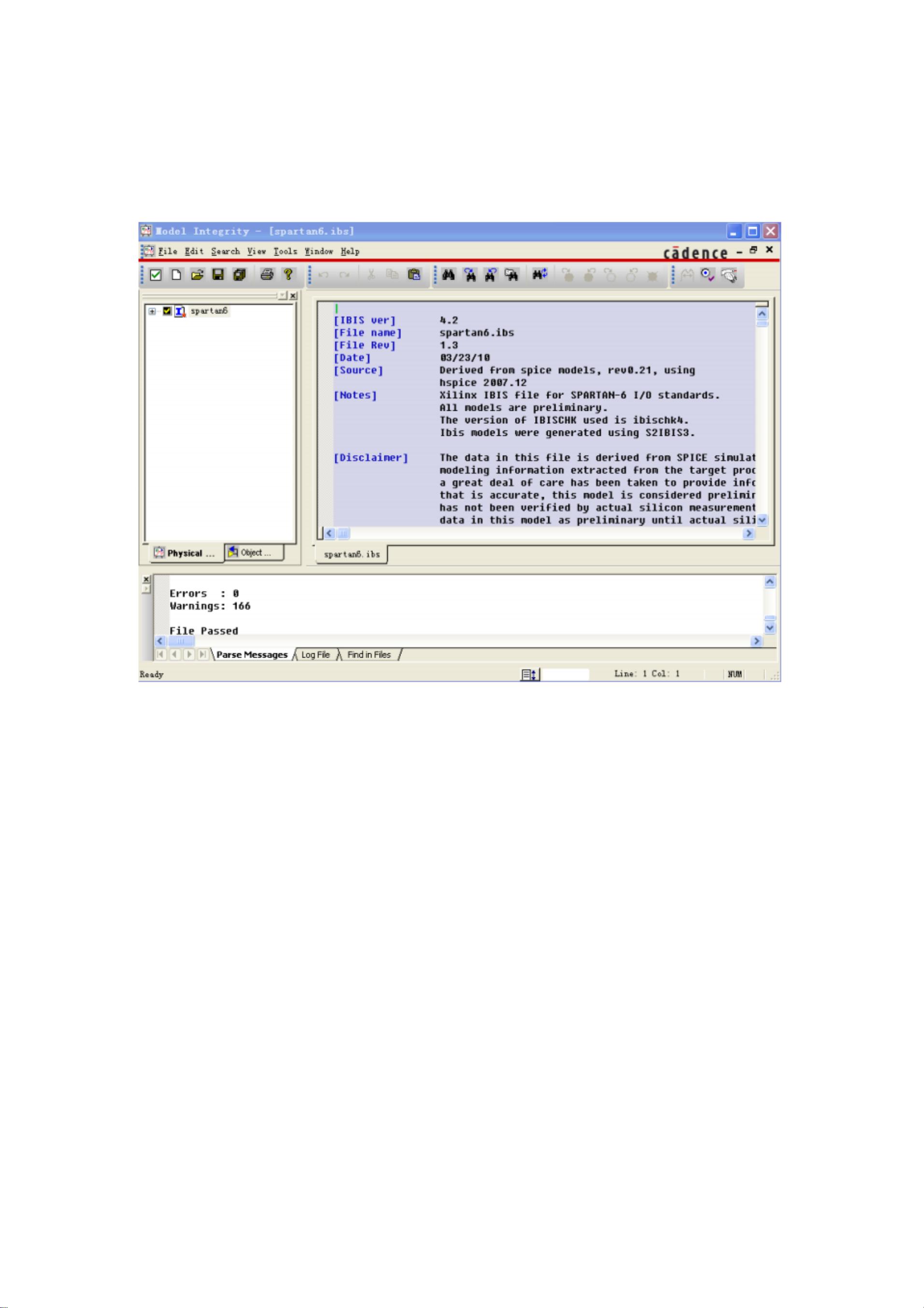

信号完整性是电子设计中的关键概念,特别是在高速数字电路中,它确保信号的质量和可靠性。本文主要关注于如何使用Cadence Allegro SI 16.3 这一高级信号完整性仿真工具来解决这些问题。Cadence Allegro SI 是一套广泛应用于电子设计自动化(EDA)领域的软件,它提供了强大的信号完整性分析功能,帮助工程师优化设计,避免潜在的信号失真和性能下降。

信号完整性问题的根源在于多个因素的综合作用,包括但不限于:反射、串扰、过冲与下冲、振荡以及信号延迟。反射是一种常见的现象,类似于光在不连续介质中的反射,它发生在信号线上传输时,由于源端和负载端阻抗不匹配导致的一部分信号能量返回。这可能导致接收数据错误或时钟问题,如不稳定的时钟边缘。正确地设计布线几何、使用合适的线端接和保持电源平面连续性是减少反射的关键。

串扰则是相邻信号线间的电磁干扰,分为感性串扰和容性串扰。感性串扰由于信号电流变化产生的交变磁场,会在邻近信号线上感应出噪声电压;容性串扰则源于信号线间的互感和互容。信号线的间距、驱动和接收端的电气特性,以及信号线的端接方式都对串扰有显著影响。Cadence Allegro SI 16.3 允许用户模拟多条耦合信号线,通过设置参数如介电常数、介质厚度、沉铜厚度、线长和宽、线间距等来评估和优化串扰效应。

在仿真过程中,工具通常需要用户指定一个受影响的信号线,以检查其他信号线对其性能的影响。这一步骤有助于识别并改正可能导致信号完整性问题的设计缺陷,例如,调整布线策略以减轻不同接收端受到的反射和串扰影响。

通过Cadence Allegro SI 16.3 进行的信号完整性仿真,不仅能够预测和量化这些现象,还能提供改进建议,以确保高速电路的信号传输精确无误,从而提高整体系统性能和稳定性。这对于现代集成电路设计来说至关重要,因为信号质量问题可能会导致系统故障、性能瓶颈或者不满足规格要求。因此,熟练掌握和应用这一工具对于电子工程师来说是一项必备技能。

363 浏览量

126 浏览量

168 浏览量

145 浏览量

209 浏览量

222 浏览量

2021-08-11 上传

weixin_38206950

- 粉丝: 0

- 资源: 1

最新资源

- StateEstimationforRobotics-CN.pdf.tar.gz

- Desktop,c语言火车票订票管理源码,c语言

- node-font-list:获取系统中安装的字体列表

- 菲尼克斯微型继电器手册.rar

- MICROMAKEL3+ 3ds chitubox插件

- Honeywell_hackathon

- developer-knowledge:独立的增强型知识项目分层清单,可以成为更好的软件开发人员。 标题

- h2gis,H2数据库的空间扩展。.zip

- NewtonJson.rar

- shell:一种用于IBM Cloud Functions and Composer的基于电子的开发工具

- 20210315-中国联通-通信行业:5G终端白皮书V4(2021年度).rar

- 单片机频率计仿真protues

- 情人节图标 .svg素材下载

- Android_Projects:我尝试学习Android开发时所做的旧项目

- 主题默认值:Hexsoftstudio CSS默认值

- Gestrue,安卓、安卓、安卓.zip