Allegro PCB设计:约束规则设置详解

需积分: 5 133 浏览量

更新于2024-07-15

1

收藏 645KB DOC 举报

"Cadence约束规则设置小结"

在电子设计自动化(EEDA)领域,Cadence Allegro是一款广泛使用的PCB布局工具。本文件主要针对Cadence Allegro 16.6和17.2版本的约束规则设置进行了详细讲解,这对于确保PCB设计的质量和效率至关重要。

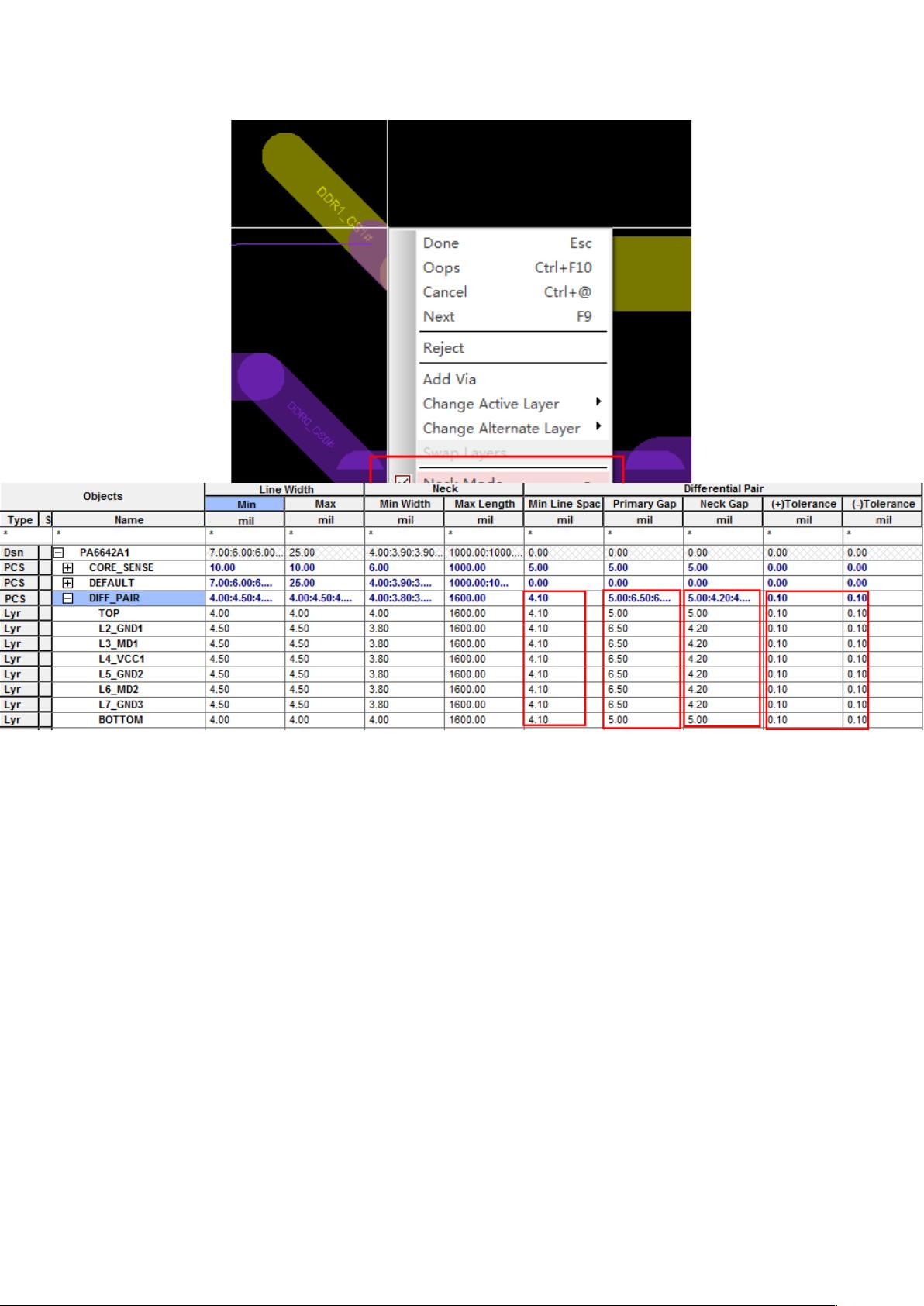

1. Physical线宽设置

线宽设置是PCB设计中的关键部分,它直接影响到信号传输的性能和完整性。在Allegro中,通过约束管理器(CM)的PhysicalConstraintSet下的All layers可以进行线宽规则的设定。通常,设计师会为不同的信号类型和阻抗需求创建定制的规则,而不仅仅依赖于默认的DEFAULT规则。

- 新增约束规则:可以通过在design名或现有规则名上右键,然后选择Create→Physical Cset来创建。如果在design名上新建,新规则会继承DEFAULT的设置;而在已有规则上新建,则会复制该规则的设置。

- 参数设置:主要包括最小线宽、最大线宽、neck mode的最小线宽和neck线宽的最大长度。最小线宽防止线宽过小导致DRC错误;最大线宽用于大电流线的处理;neck mode最小线宽用于特殊区域的线宽控制;neck线宽的最大长度确保neck模式下的线宽适应性。

2. 差分线宽约束

差分线对信号传输速度和抗干扰能力有显著提升。在Allegro中,差分线的约束规则更复杂,除了基本的线宽外,还包括差分对两根线之间的间距。

- Primary Gap:差分对两根线的默认间距。

- Neck Gap:在neckmode下,差分线之间的间距。

- Tolerance:由于实际布线时的微小偏差,需要设置容差值,以避免因间距不精确产生的DRC错误。

3. 约束规则的重要性

正确设置约束规则能有效提高设计效率,避免设计过程中出现DRC (Design Rule Check) 错误,并确保设计符合电气和物理规范。这有助于在设计早期发现并解决潜在问题,从而减少后期修改的次数,缩短产品上市时间。

4. 应用场景

在BGA区域,由于空间限制,可能需要采用更小的线宽,这时可利用neck mode功能,调整特定区域的线宽规则,以满足设计要求。

理解并熟练应用Cadence Allegro的约束规则设置是PCB设计工程师必备的技能之一。通过精细化的规则配置,可以实现高效且高质量的PCB设计,满足各种复杂的信号传输和电磁兼容性要求。

437 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

团子她老爸

- 粉丝: 0

- 资源: 5

最新资源

- 两个环信聊天demo.7z

- Pytorch_tutorial

- 二进制时钟:以二进制表示显示时钟时间-matlab开发

- poketcg:神奇宝贝TCG的拆卸

- ShipMMGmodel.zip

- typora-setup-x64.rar

- Hackernews-Node

- U12_Windows_Driver.zip

- 职业危害防治管理规章制度汇编

- 语境

- 安卓QQ聊天界面源代码

- Gardeningly - Latest News Update-crx插件

- calculator:使用 javascript 构建基本计算器

- JavaCalculatorApplication

- bnf:解析BNF语法定义

- COSC-350