FPGA时序优化:基于outputdelay的IO约束解析

版权申诉

"FPGA基于outputdelay的IO约束实例分析,主要关注如何在FPGA开发中解决源同步电路的时序问题,尤其是通过outputdelay进行IO约束来优化设计。"

在FPGA开发中,源同步电路的设计往往面临挑战,因为数据和时钟必须独立地传输到目标芯片。通常,数据和时钟会通过ODDR(Output Delayed Data Register)分开输出,但这可能导致工程在时序收敛时出现问题,尤其是在实际硬件上运行时。这些问题的根本原因包括:

1. FPGA内部不同环境条件(Corner)下的器件延迟差异,特别是缓冲器(BUF)。

2. 数据和时钟在板级传输时的线路延迟误差。

3. 目标芯片的建立时间和保持时间要求。

4. 目标芯片的阈值电压差异。

为了解决这些问题,有两种常用的方法:时钟相位偏移和数据通道添加output delay。时钟相位偏移是通过PLL(Phase-Locked Loop)产生相位不同的两路时钟,通过实验调整相位差以满足后级芯片的时序要求,但这种方法调整不够精确。另一方面,output delay利用FPGA的IOB资源中的延迟单元,可以精确控制输出延迟,与板级布线延迟和目标芯片的寄存器建立保持时间相结合,通过Vivado等工具进行约束,以确保设计的准确性。然而,这种方法需要提前知道所有相关的参数和延迟,否则约束可能会不正确。

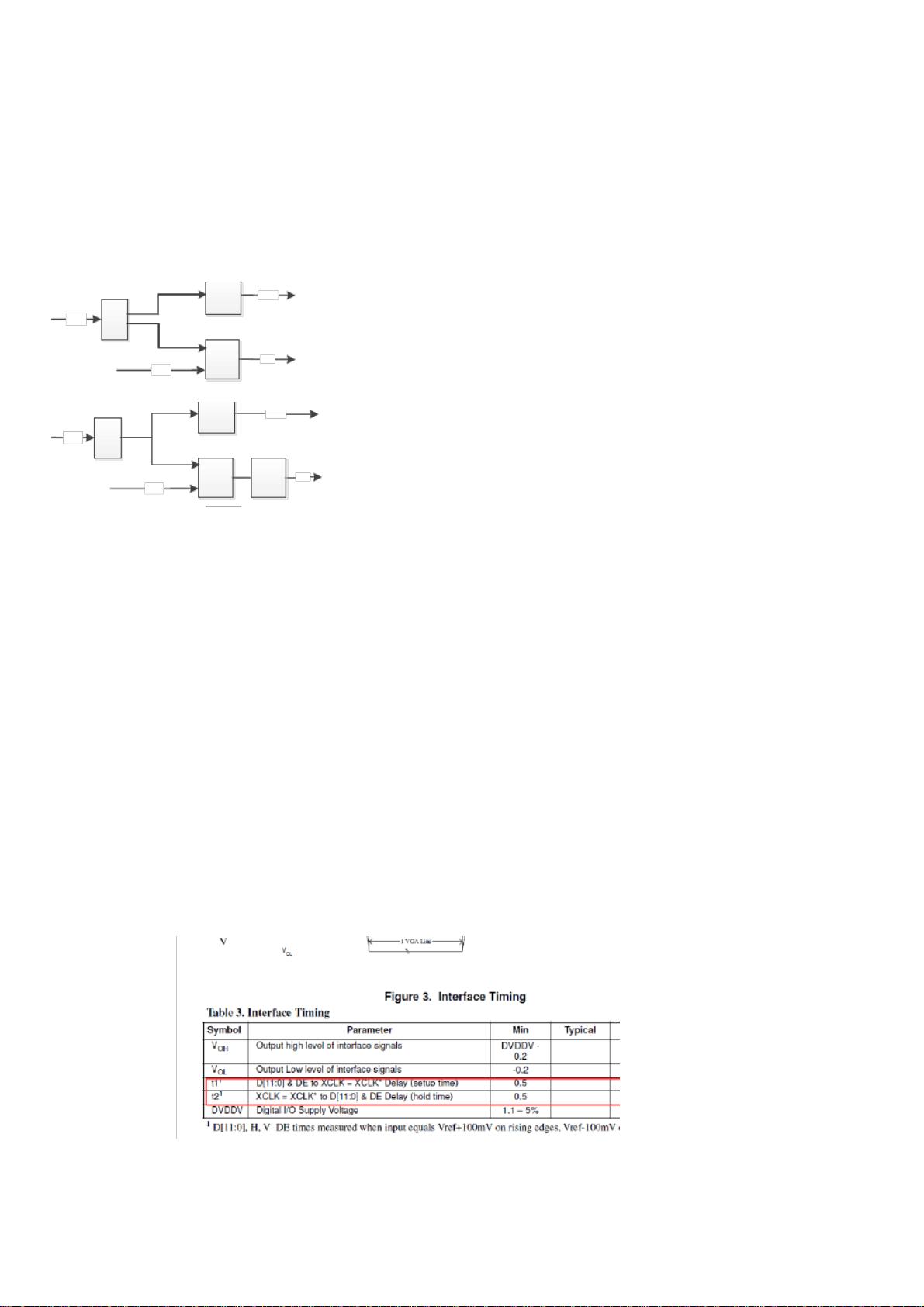

本文重点讨论的是通过output delay的方法。在一个具体的实例中,为了节省I/O资源,视频输出的24bit数据被缩减为12bit,这需要使用ODDR实现双沿采样。在这种情况下,由于1080p的像素时钟为148.5MHz,ODDR的采样率接近300MHz。设计中,50MHz的晶振时钟通过INBUF进入MMCM(Multi-Mode Clock Manager)生成148.5MHz的像素时钟,分别驱动时钟和数据路径的ODDR。数据路径中额外增加了delay,然后经过OBUF输出,最终通过板级走线传输到目标芯片CH73。

这个实例展示了output delay的实际应用,即通过调整数据路径的延迟,使其与时钟路径分离一段特定时间,以补偿线路延迟和器件误差,从而满足目标芯片的建立和保持时间要求。这种方法更精确,但也需要更详尽的前期规划和参数了解。通过理解这些原理和技术,开发者可以更好地处理FPGA设计中的源同步电路时序问题,确保设计的稳定性和可靠性。

2021-10-11 上传

2024-03-28 上传

2023-09-16 上传

2021-07-13 上传

2021-07-13 上传

_webkit

- 粉丝: 31

- 资源: 1万+

最新资源

- MATLAB新功能:Multi-frame ViewRGB制作彩色图阴影

- XKCD Substitutions 3-crx插件:创新的网页文字替换工具

- Python实现8位等离子效果开源项目plasma.py解读

- 维护商店移动应用:基于PhoneGap的移动API应用

- Laravel-Admin的Redis Manager扩展使用教程

- Jekyll代理主题使用指南及文件结构解析

- cPanel中PHP多版本插件的安装与配置指南

- 深入探讨React和Typescript在Alias kopio游戏中的应用

- node.js OSC服务器实现:Gibber消息转换技术解析

- 体验最新升级版的mdbootstrap pro 6.1.0组件库

- 超市盘点过机系统实现与delphi应用

- Boogle: 探索 Python 编程的 Boggle 仿制品

- C++实现的Physics2D简易2D物理模拟

- 傅里叶级数在分数阶微分积分计算中的应用与实现

- Windows Phone与PhoneGap应用隔离存储文件访问方法

- iso8601-interval-recurrence:掌握ISO8601日期范围与重复间隔检查