数字电路与逻辑设计:组合逻辑电路设计方法与应用

版权申诉

146 浏览量

更新于2024-07-02

收藏 2.15MB PDF 举报

数字电路与逻辑设计:CH3 组合逻辑电路

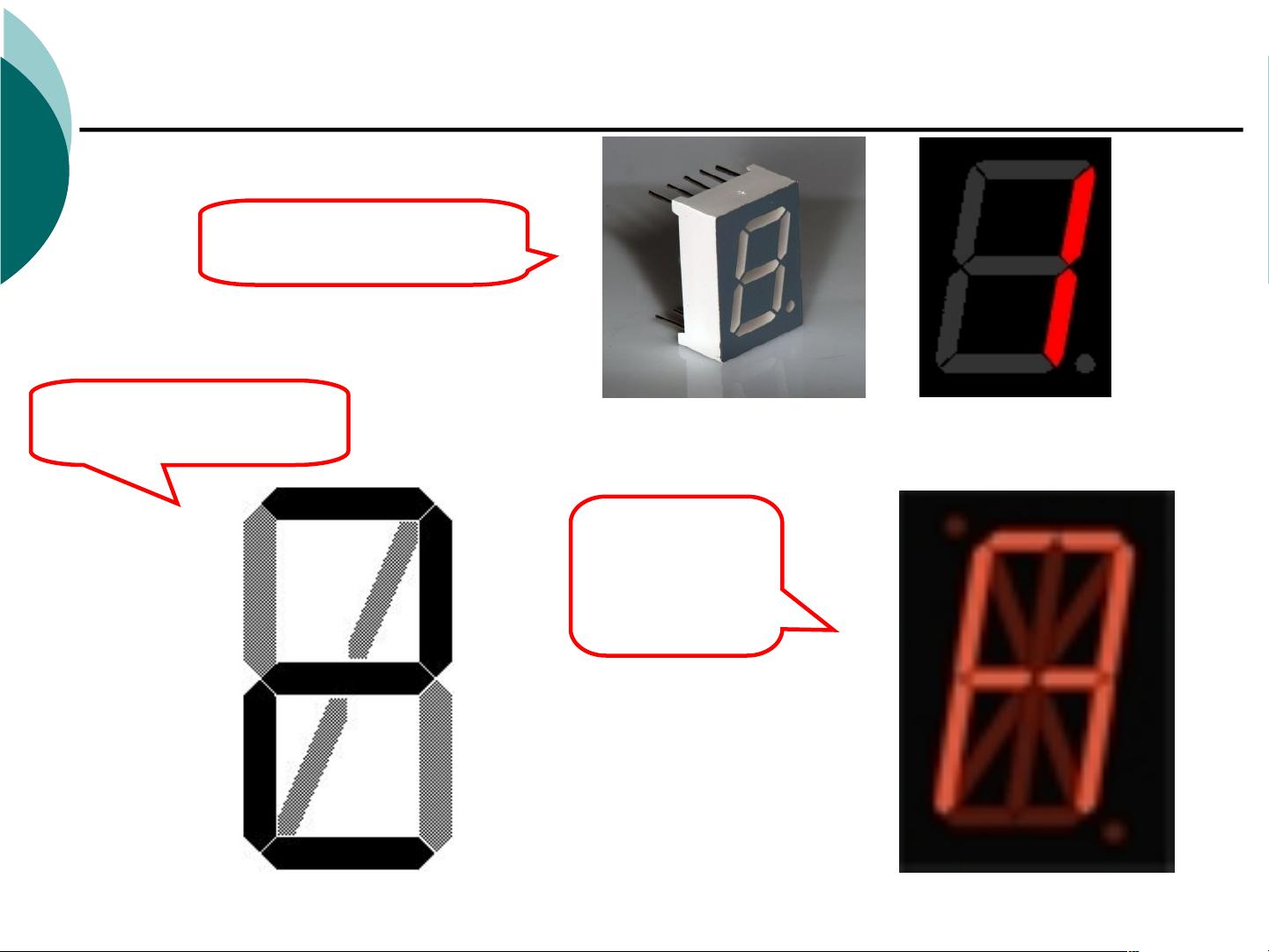

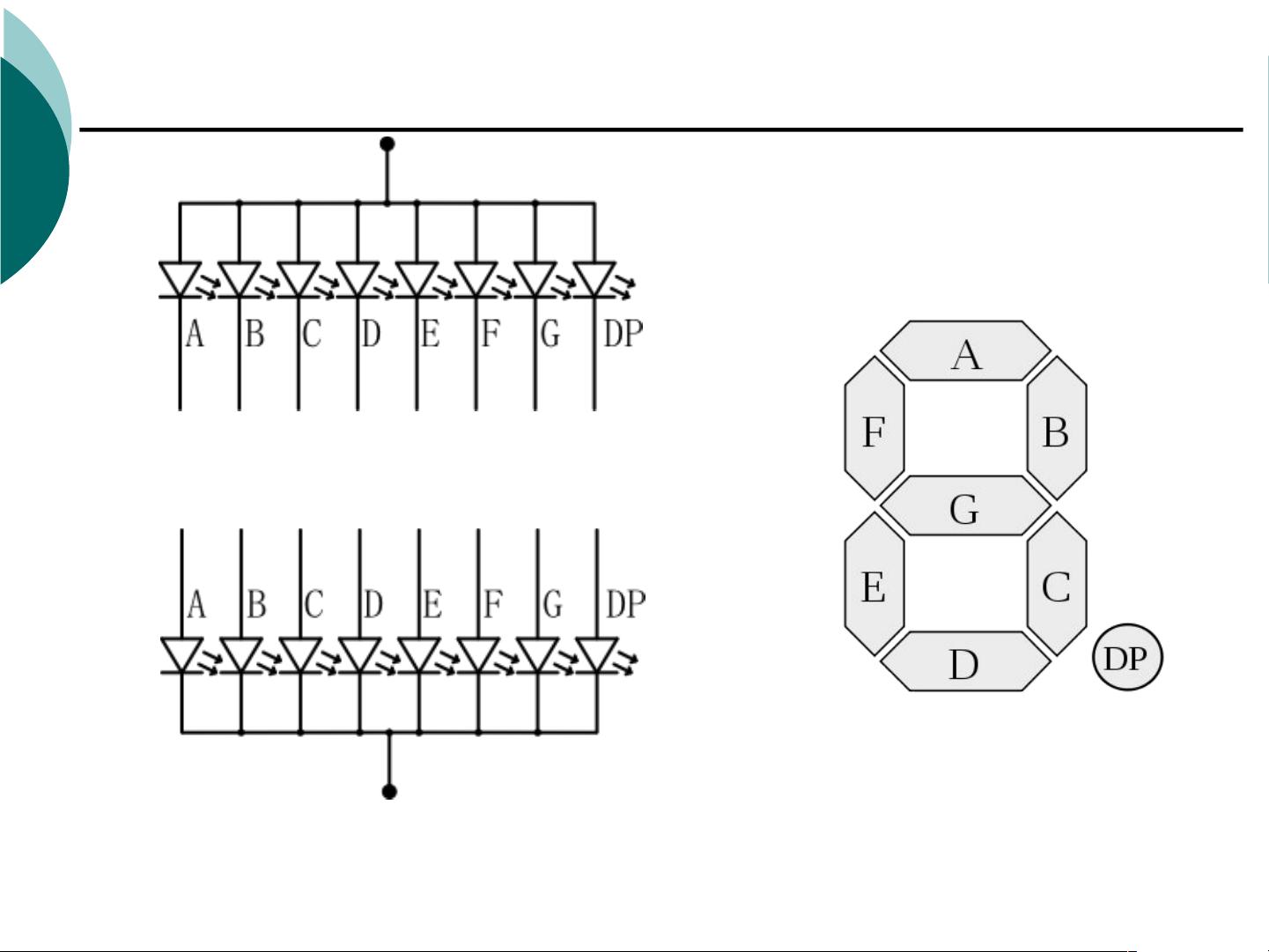

数字电路与逻辑设计是计算机科学和电子工程中的一门重要课程,本章节主要讲述组合逻辑电路的设计和实现。组合逻辑电路是一种基本的数字电路结构,它的输出仅取决于当前输入信号的状态,不具有记忆功能。

数字电路的设计过程可以分为五个步骤:实际问题、逻辑问题、抽象、数学问题、变换、逻辑代数解、求解、逻辑电路、变换、实际电路、细化。其中,逻辑代数解是指使用布尔代数来描述逻辑电路的行为。

组合逻辑电路的特点有四个:任意时刻的稳态输出仅取决于该时刻输入变量的状态;在电路结构上信号流向是单向的;一般由逻辑门构成,不含记忆元件;输出与输入之间存在一定的延迟时间。

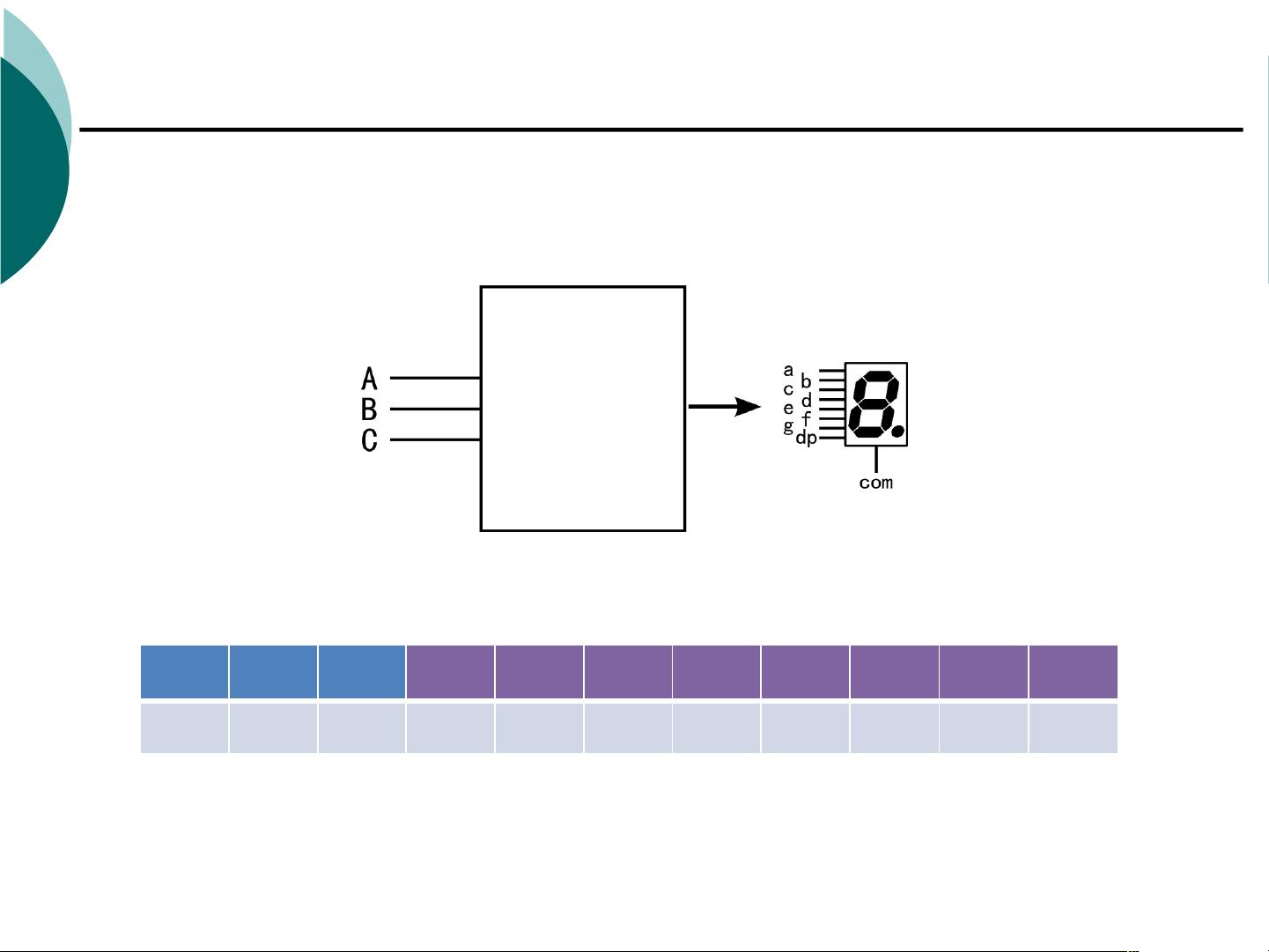

在设计组合逻辑电路时,需要根据实际问题确定输入、输出变量,并定义逻辑状态的含义。然后,根据输入、输出的因果关系,列出真值表,并由真值表写出逻辑表达式,根据需要简化和变换逻辑表达式。最后,画出逻辑图。

在本章节中,我们将通过两个例子来说明组合逻辑电路的设计。第一个例子是设计一个轿车告警电路,当车门没有关好且发动机已经启动时,或者当司机没有系安全带且车速超过30km/h时,发出告警信号。第二个例子是设计一个三路表决器,根据少数服从多数原则输出结果。

在设计组合逻辑电路时,需要使用逻辑代数来描述逻辑电路的行为。逻辑代数是一种数学工具,用于描述逻辑电路的行为。我们可以使用布尔代数来描述逻辑电路的行为,并使用摩根律来化简逻辑函数。

在VerilogHDL中,我们可以使用module语句来描述逻辑电路的行为。例如,在设计一个三路表决器时,我们可以使用以下代码来描述逻辑电路的行为:

```verilog

module decide3(a, b, c, f);

input a, b, c;

output f;

nand u1(t1, a, b);

nand u2(t2, a, c);

nand u3(t3, b, c);

nand u4(f, t1, t2, t3);

endmodule

```

组合逻辑电路是数字电路设计的基础,它的设计需要根据实际问题确定输入、输出变量,并使用逻辑代数来描述逻辑电路的行为。

2022-06-22 上传

2022-06-22 上传

2022-06-22 上传

2023-09-13 上传

2024-04-22 上传

2024-07-05 上传

2023-09-14 上传

2023-06-13 上传

2023-06-05 上传

2023-05-28 上传

wxg520cxl

- 粉丝: 25

- 资源: 3万+

最新资源

- 火炬连体网络在MNIST的2D嵌入实现示例

- Angular插件增强Application Insights JavaScript SDK功能

- 实时三维重建:InfiniTAM的ros驱动应用

- Spring与Mybatis整合的配置与实践

- Vozy前端技术测试深入体验与模板参考

- React应用实现语音转文字功能介绍

- PHPMailer-6.6.4: PHP邮件收发类库的详细介绍

- Felineboard:为猫主人设计的交互式仪表板

- PGRFileManager:功能强大的开源Ajax文件管理器

- Pytest-Html定制测试报告与源代码封装教程

- Angular开发与部署指南:从创建到测试

- BASIC-BINARY-IPC系统:进程间通信的非阻塞接口

- LTK3D: Common Lisp中的基础3D图形实现

- Timer-Counter-Lister:官方源代码及更新发布

- Galaxia REST API:面向地球问题的解决方案

- Node.js模块:随机动物实例教程与源码解析