Cyclone V SoC FPGA器件硬核处理器系统详解

"Altera的Cyclone V SoC FPGA器件包含了一个硬核处理器系统(HPS)和FPGA,是集成了高性能处理与可编程逻辑的单芯片解决方案。本手册为第一章,介绍了HPS的基本概念和功能。"

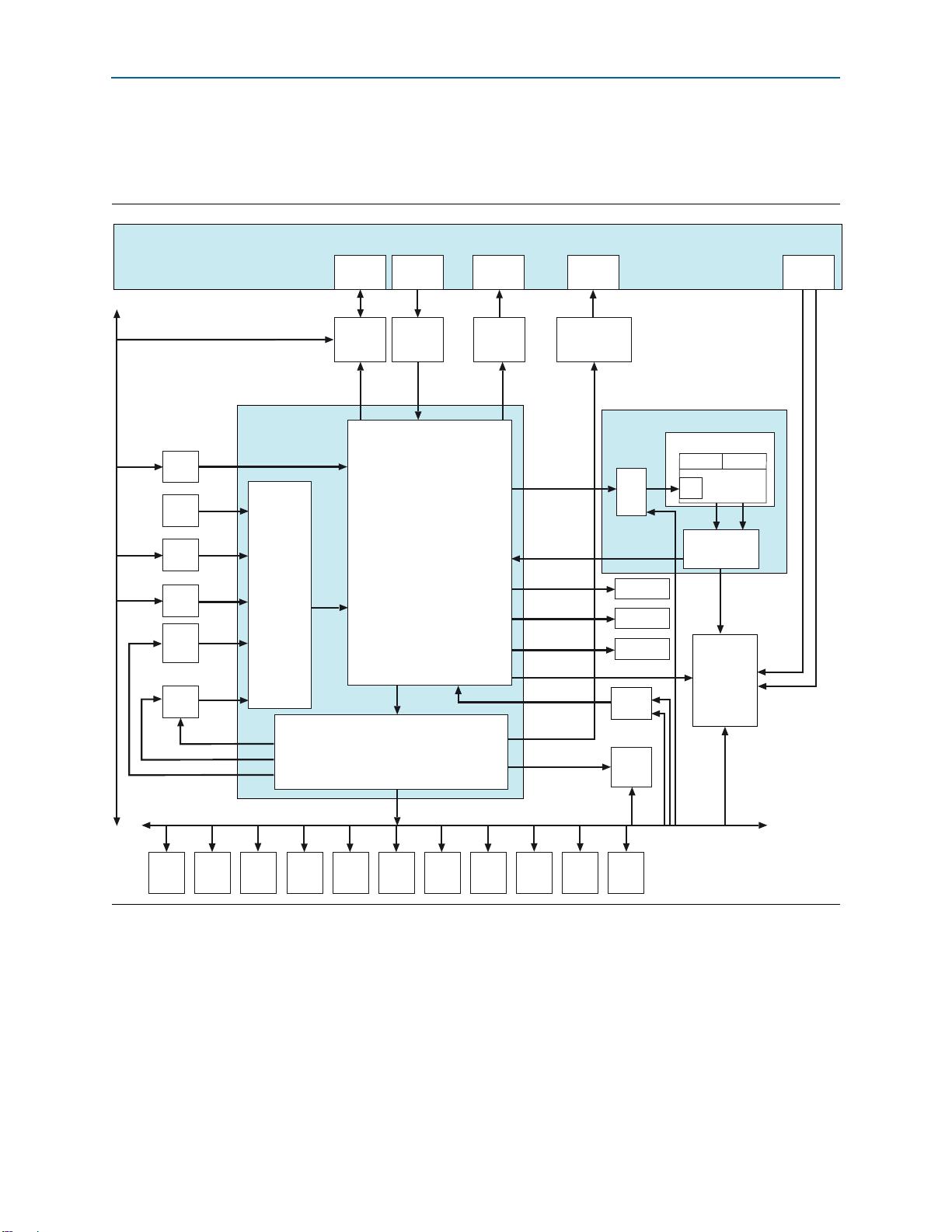

在Altera的Cyclone V SoC FPGA器件中,硬核处理器系统(HPS)是一个关键组成部分,它整合了高性能的处理能力与灵活的FPGA逻辑,实现了硬件加速和系统级优化。HPS主要包括了基于ARM架构的处理器,如ARM Cortex-A9双核或四核处理器,能够执行复杂的操作系统和应用程序,处理大量的数据处理任务。

HPS的主要功能包括:

1. **处理器核心**:基于ARM Cortex-A9的双核或四核处理器,支持多线程、浮点运算和高级指令集,适用于运行实时操作系统(RTOS)和嵌入式Linux等。

2. **内存接口**:HPS提供对DDR3/DDR3L SDRAM的直接访问,以高速缓存和存储大量数据,满足高性能计算需求。

3. **外设接口**:HPS集成了多种标准外设接口,如PCI Express、千兆以太网、USB、SPI、I2C、GPIO等,方便连接各种外部设备。

4. **互连结构**:HPS内部有高性能的AXI总线,用于处理器、内存控制器以及外设之间的数据传输,确保高效的数据流。

5. **安全特性**:HPS提供了安全功能,如加密引擎、安全调试和信任根,以保障系统的安全性和完整性。

6. **集成的硬件加速器**:部分HPS设计可能包含特定的硬件加速器,如数字信号处理器(DSP)块,用于特定算法的加速。

与HPS并存的FPGA部分提供了高度可编程的逻辑资源,可以定制实现各种功能,如协议转换、数据预处理、后处理,以及与HPS的通信接口。FPGA可以动态调整,以适应不断变化的应用需求,实现灵活性和性能的平衡。

Cyclone V SoC FPGA器件的这一设计使得开发者能够将处理器的高效率和FPGA的灵活性结合起来,实现低功耗、高性能的系统设计。开发者可以利用Altera的Quartus II软件进行综合、布局布线和编程,实现HPS与FPGA的协同工作。

在应用Cyclone V SoC FPGA时,设计人员应关注HPS和FPGA之间的接口,确保数据交换的高效性和实时性。此外,了解最新的器件规格和文档,以确保设计符合最新的标准和要求,是至关重要的。Altera提供的技术参考手册详细阐述了HPS的架构、配置、编程和调试方法,为开发者提供了全面的指导。

相关推荐

Pual_Xia

- 粉丝: 1

- 资源: 7

最新资源

- 维修中心产品报价清单excel模版下载

- lsvine:`tree -L 2`具有较少的空白屏幕空间

- project_app:这是非常重要的项目

- Newton's method done right:牛顿法求解非线性方程组,包括非平方和不一致方程组-matlab开发

- 现代客厅模型效果图

- 美丽的心型:用Python表达爱意

- command-line-linter

- simpleMapExercise

- SpotifyStalker

- 日记账格式excel模版下载

- dfs:DFS 阵容优化器应用程序的 Github 存储库

- WebProjectWithDjango

- DEF-CON-Links:DEF CON 28安全模式的简易链接和指南

- r7rs-clos:适用于R7RS的微型CLOS包装器

- 小型电影院3D模型

- vscode_ros2