Verilog基础教程:快速学习硬件描述语言

需积分: 9 12 浏览量

更新于2024-07-18

收藏 1.43MB PDF 举报

"这篇资源是关于Verilog基础教学的文档,旨在帮助初学者快速掌握Verilog编程语言。Verilog是一种硬件描述语言(HDL),它使用类似C语言的语法来描述电子电路的功能和结构,支持在不同的抽象层级上描述电路,并能表达并行性。文档中提到了Verilog和VHDL两种主要的HDL,指出Verilog由于其C语言背景,学习曲线较为平缓。此外,文档还包含了一个简单的Verilog实例——边沿触发型D触发器的实现,以及Verilog HDL的基本要素和标识符规则。"

在Verilog语言中,硬件描述语言(HDL)的作用是将电路的逻辑功能以编程的形式表示出来,允许设计者在软件环境中描述硬件行为。Verilog的特殊结构使得它可以描述电路的连接、功能、时序,同时适应并行处理的需求。作为两种主要的HDL之一,Verilog与C语言有较强的相似性,这使得对于熟悉C语言的人来说,学习Verilog更为方便。相比之下,VHDL虽然标准化较早,但其格式要求严格,学习难度相对较大。

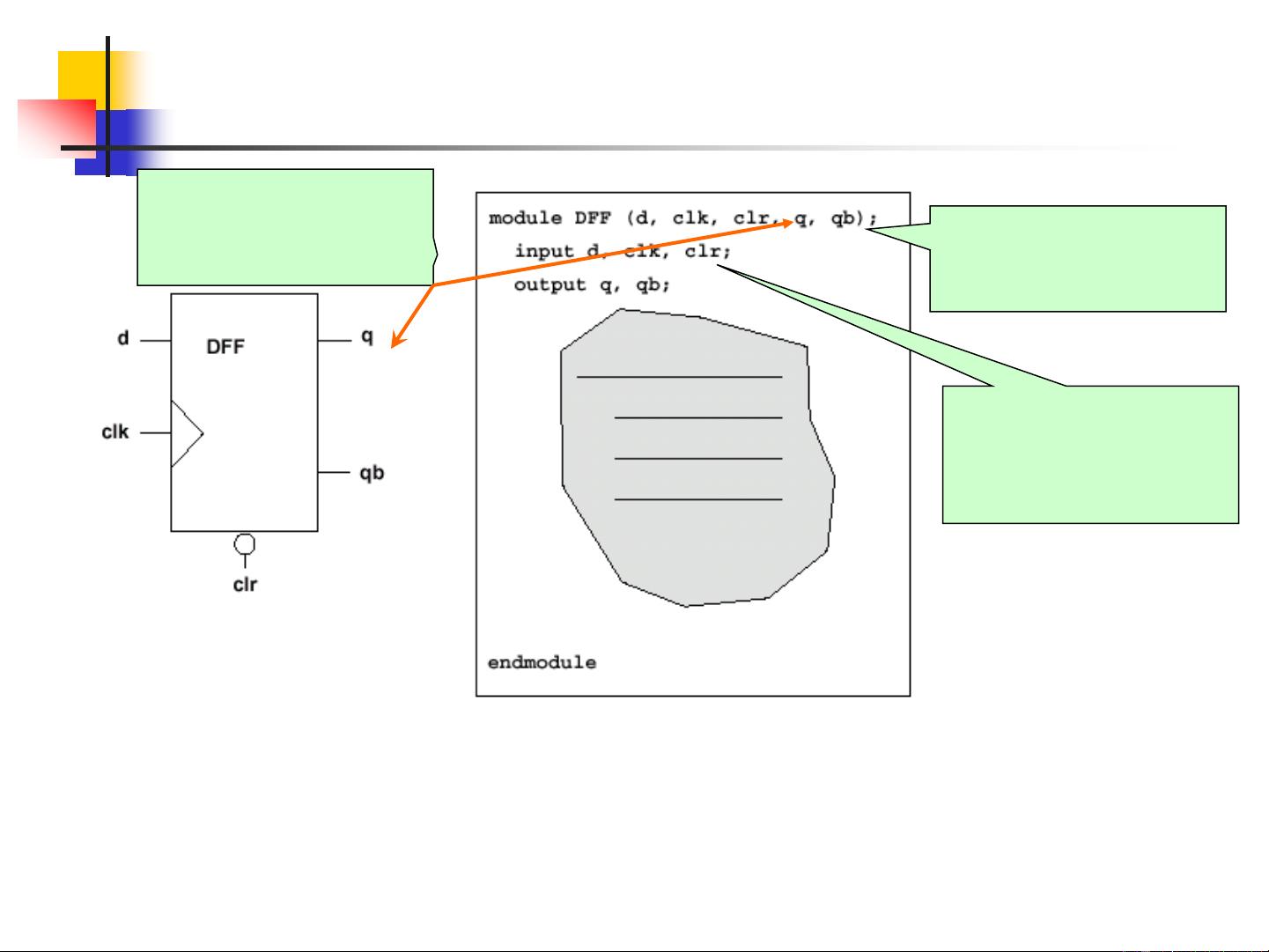

文档中给出的Verilog实例是一个D触发器的模块定义,`module DFF(d, clk, q);`表示DFF模块,有输入`clk`和`d`,输出`q`,`reg q;`声明`q`为寄存器类型。`always @(posedge clk)`监听时钟的上升沿,当`clk`上升沿到来时,执行`q <= d;`,将`d`的值锁入`q`,完成触发器的功能。

Verilog HDL的基本要素包括标识符、语句结构、注释和时间规范等。标识符的命名规则非常重要,必须以字母或下划线开头,后续可以是字母、数字、美元符号或下划线,且区分大小写。关键词必须小写以避免冲突。注释分为单行`//`和多行`/* */`两种。时间规范则主要用于仿真过程中的时间控制。

在编写Verilog代码时,有一些最佳实践需要遵循,例如使用有意义的名称,用下划线分隔单词,使用前缀或后缀来明确信号的类型,保持信号名称的一致性,以及使用大写字母表示参数等。这些规则有助于提高代码的可读性和可维护性。

这篇文档是Verilog初学者的良好起点,它涵盖了语言的基础概念、基本元素以及编写规范,有助于读者快速入门并逐步掌握Verilog编程。

2010-05-11 上传

2025-01-05 上传

107 浏览量

2008-09-25 上传

2014-08-21 上传

627 浏览量

qq_37636641

- 粉丝: 0

- 资源: 2

最新资源

- 关于sql优化.doc

- 服装行业电子商务平台建设构想.pdf

- JAVA解惑之详细介绍

- sql server 2000

- Java项目开发常见问题分析

- accp5.0s2三层+OOP测试

- css常用参数说明文档

- Websphere Appliction Server Development Best Practices for Performance and Scalability.pdf

- 高质量C++编程指南.pdf

- FastReport_3.0_设计手册PDF

- The_C_Programming_Language_2nd_edition

- Test Automation Frame--主要框架的介绍.doc

- tuxedo编程速成

- JBossWeb用户手册

- PHP5与MySQL5 Web开发技术详解.pdf

- 很好的linux学习笔记