IAR编译器在MAXQ微控制器上的闪存SRAM管理

98 浏览量

更新于2024-08-28

收藏 279KB PDF 举报

"利用IAR编译器分配MAXQ®微控制器上的闪存和SRAM存储器"

在嵌入式系统开发中,有效地管理和利用微控制器的内存资源是至关重要的。MAXQ系列微控制器,以其独特的Harvard架构和高效能RISC指令集,为开发者提供了强大的处理能力。本应用笔记主要探讨了如何利用IAR Embedded Workbench工具来分配和访问MAXQ微控制器上的闪存和SRAM存储器。

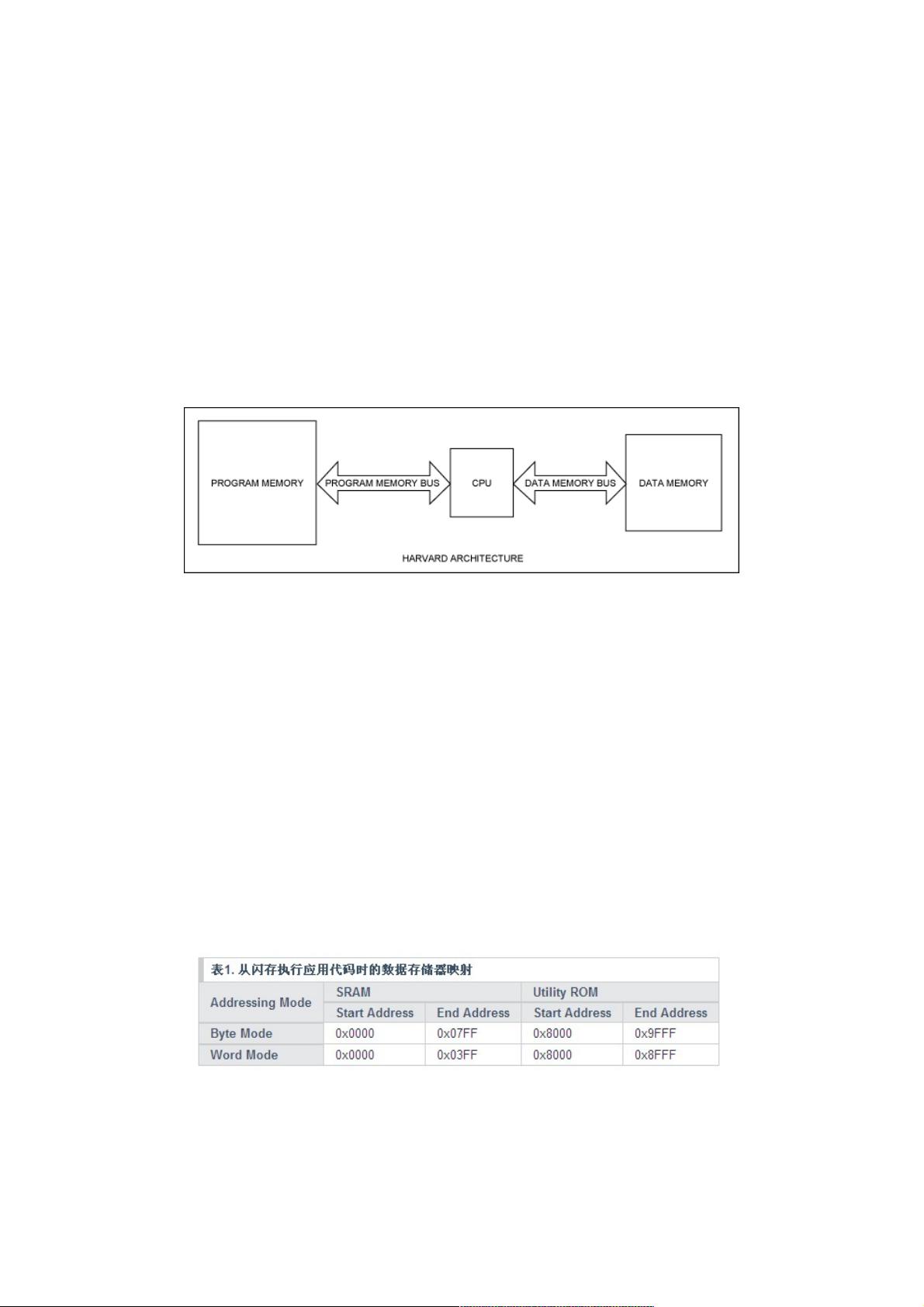

MAXQ微控制器的架构基于Harvard结构,这是一种将程序和数据存储器分开的体系,使得程序和数据可以同时在独立的总线上读取,从而实现单周期指令执行。这样的设计显著提高了处理器的效率,因为数据总线和指令总线不会互相冲突。每个MAXQ器件包括三种类型的存储器:闪存、SRAM以及固定用途的ROM。这些存储器各自有不同的功能和应用场景。

1. 闪存:用于存储程序代码和可配置的非易失性数据。在MAXQ微控制器中,尽管不能直接对闪存进行读写操作,但可以通过固定用途的ROM函数来实现数据的存取。这些ROM函数的起始地址已经集成在IAR编译器中,便于开发者调用。

2. SRAM:作为高速的随机存取内存,用于存储程序运行时的临时数据和变量。在从闪存执行程序时,SRAM通常被用作数据存储器,供读写操作使用。

3. 固定用途ROM:包含一些预先定义好的、不可修改的函数,用于执行特定的任务,如对闪存的读写操作。这些函数的地址是固定的,可以直接由CPU调用,无需通过程序存储器。

在使用IAR Embedded Workbench进行开发时,开发者需要明确指定程序和数据的存储位置。例如,当程序从闪存执行时,SRAM用于数据存储,而固定用途ROM则作为只读数据源。表1和图2分别提供了详细的存储器映射信息,帮助开发者理解不同存储区域的布局和使用方式。

在实际编程过程中,IAR编译器会自动处理内存分配,但开发者仍然需要了解如何在代码中正确地声明和访问这些内存区域。例如,全局变量和静态变量通常会被放置在指定的内存区域,而局部变量通常在栈上分配。为了优化性能,开发者还可以使用特定的编译器指令或宏来控制变量的存储位置。

此外,对于需要在非易失性闪存中保存数据的情况,开发者可以利用固定用途ROM中的读写函数,这些函数提供了安全且高效的方法来存取闪存数据,而不会影响程序的正常执行。确保正确理解和使用这些函数是成功开发MAXQ微控制器应用的关键。

总结来说,理解MAXQ微控制器的内存架构以及如何利用IAR Embedded Workbench进行内存管理是提高系统效能和可靠性的基础。通过熟练掌握这些技巧,开发者能够充分利用MAXQ微控制器的各项特性,创建高效、稳定且适应性强的嵌入式应用。

2014-03-21 上传

2024-01-26 上传

2023-07-27 上传

2023-09-01 上传

2023-05-02 上传

2023-09-06 上传

2023-07-01 上传

2023-04-02 上传

weixin_38732315

- 粉丝: 7

- 资源: 963

最新资源

- 李兴华Java基础教程:从入门到精通

- U盘与硬盘启动安装教程:从菜鸟到专家

- C++面试宝典:动态内存管理与继承解析

- C++ STL源码深度解析:专家级剖析与关键技术

- C/C++调用DOS命令实战指南

- 神经网络补偿的多传感器航迹融合技术

- GIS中的大地坐标系与椭球体解析

- 海思Hi3515 H.264编解码处理器用户手册

- Oracle基础练习题与解答

- 谷歌地球3D建筑筛选新流程详解

- CFO与CIO携手:数据管理与企业增值的战略

- Eclipse IDE基础教程:从入门到精通

- Shell脚本专家宝典:全面学习与资源指南

- Tomcat安装指南:附带JDK配置步骤

- NA3003A电子水准仪数据格式解析与转换研究

- 自动化专业英语词汇精华:必备术语集锦