FPGA实现的DPLL位同步时钟提取技术在EDA/PLD中的应用

186 浏览量

更新于2024-08-30

1

收藏 382KB PDF 举报

"EDA/PLD中的基于FPGA的提取位同步时钟DPLL设计"

在数字通信系统中,位同步技术是确保数据正确传输的关键,它涉及到接收端的时钟与发送端保持精确同步,从而正确解码接收到的码元。位同步时钟信号在系统的多个环节中起到关键作用,包括码元监测、帧同步以及码元的解调和判决。位同步技术主要分为外同步法和自同步法。

外同步法需要额外传输位同步信息,即接收端通过专门的同步信号来调整自己的时钟,这种方法简单但依赖于可靠的同步信道,当同步信道受到干扰时,可能导致同步失效。

自同步法则更加常见,因为它可以从已传输的数据中直接提取位同步信息。自同步法又可分为开环同步和闭环同步。开环同步不依赖于反馈,而是通过对输入码元进行某种变换来估计位同步信息,但这种方法可能不够准确。相比之下,闭环同步通过比较本地时钟与输入信号的相位差,并利用反馈机制调整本地时钟,从而实现更精确的锁定,这种方法被广泛应用于实际系统中。

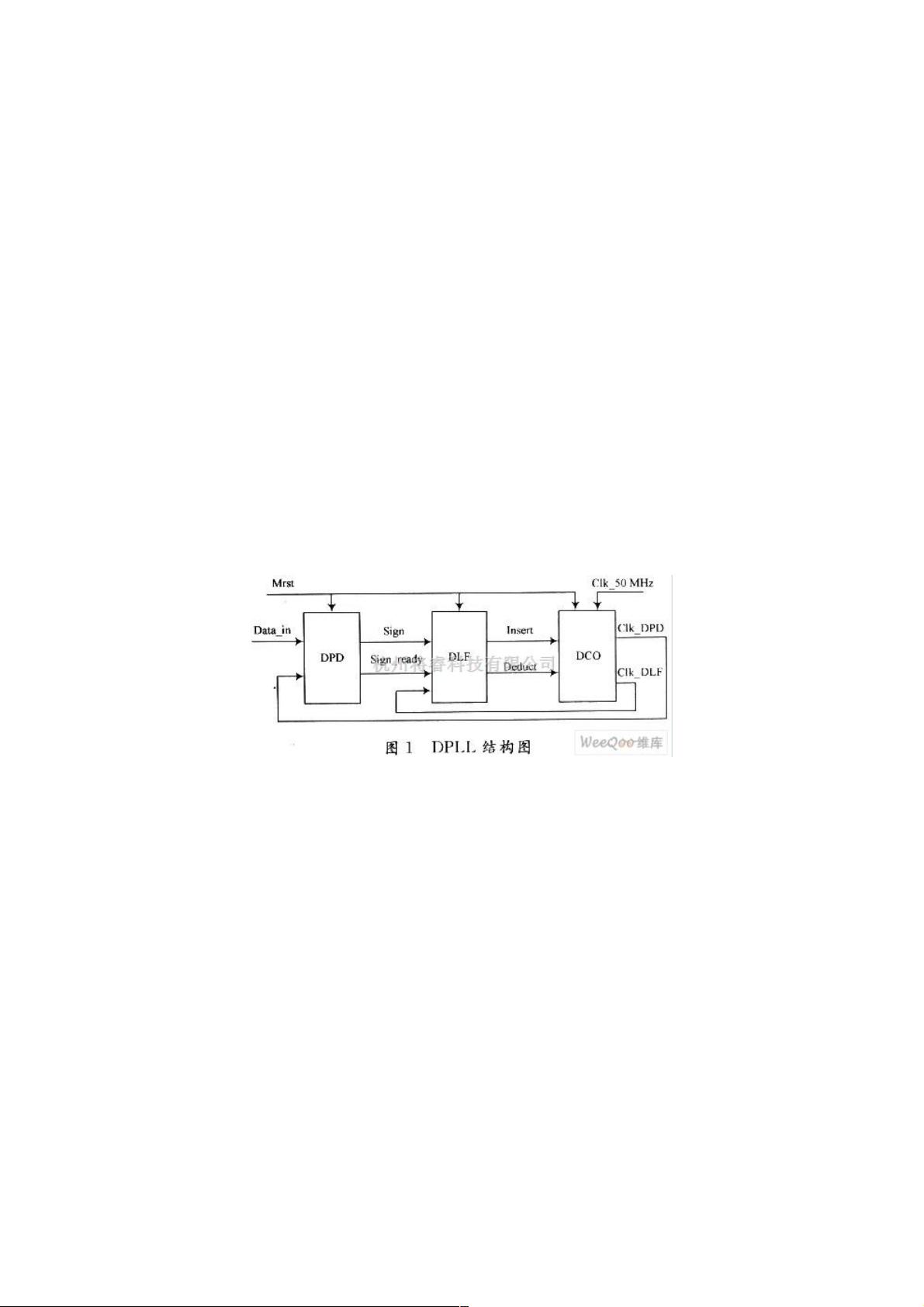

本文关注的是基于FPGA的自同步法,特别是采用全数字锁相环(DPLL)实现位同步时钟提取。DPLL是一种闭环系统,它包括鉴相器、压控振荡器(VCO)和分频器等组成部分。鉴相器比较输入码元与本地时钟的相位,然后通过VCO调整本地时钟的频率,分频器则控制调整的步长。

在本设计中,DPLL采用了超前-滞后结构,能够根据鉴相器的判断,通过加减门控制相位调整,使得本地时钟逐渐接近输入码元的相位。然而,这样的系统在连续相同码元(连“1”或连“0”)时可能会遇到锁定时间较长的问题,这限制了同步建立时间和调整精度。尽管如此,由于DPLL的自我调节能力,即使在码元丢失或相位抖动的情况下,仍能输出相对稳定的同步脉冲。

由于设计应用于地铁车辆总线的通信系统,传输速率较低(250Kb/s),使用曼彻斯特编码,这种DPLL方案能够满足系统的需求,确保在低速通信环境下实现稳定且准确的位同步。基于FPGA的DPLL设计为实现位同步提供了一种实用的解决方案,尤其适用于需要高精度和自我恢复能力的通信环境。

2020-10-26 上传

2020-11-08 上传

2020-10-22 上传

2020-10-21 上传

2020-12-09 上传

2020-12-10 上传

2020-11-05 上传

2020-11-08 上传

2020-10-20 上传

weixin_38632916

- 粉丝: 4

- 资源: 964

最新资源

- 深井潜水泵电缆线接头的密封.rar

- 风险评估方案 和详细评估方法

- stevenjpr

- Accuinsight-1.0.17-py2.py3-none-any.whl.zip

- mipaka

- 网址模板

- WebAppDemo.zip

- Collumned NPR-crx插件

- Add to uStart (by uStart)-crx插件

- Gamers-Systems:所有游戏玩家的应用

- quickcheck:R 的随机测试

- 工作库:由学生完成的项目,为隆德大学LTH的ETSF20课程

- tour-mobile

- Feedly Subscriber-crx插件

- misc

- multiplayer_snake_game