FPGA高层次综合:MATLAB、VIVADO HLS与OpenCL在数字信号处理中的应用

需积分: 10 168 浏览量

更新于2024-07-16

收藏 1.45MB DOCX 举报

本文主要探讨的是基于FPGA的数字信号处理方法,特别关注Altera DSP Builder如何结合The MathWorks MATLAB和Simulink的算法开发工具,以实现高性能的数字信号处理平台。FPGA(Field Programmable Gate Arrays)因其灵活性、高效率和可靠性,逐渐成为数字信号处理的理想选择,特别是在不牺牲设计灵活性的前提下,能够提供比通用DSP更好的性能。

传统的FPGA设计流程包括物理级、寄存器传输级(RTL)、行为级和系统级设计,而高层次综合(HLS)作为一种新兴技术,允许算法和软件工程师使用诸如C/C++、Matlab等高级语言进行设计,避免直接接触复杂的硬件描述语言(HDL)。HLS通过自动将高级语言代码转化为可编程逻辑,简化了设计过程,使得不具备硬件背景的专业人员也能参与到FPGA项目中。

Xilinx的VIVADO HLS是这类工具的一个例子,它提供了一个易用的接口,使得开发者能利用标准处理器或专用硬件进行算法优化。通过VIVADO HLS,设计师可以在系统级别描述算法,然后编译器负责转换为适合FPGA实现的底层逻辑。这不仅提高了设计效率,还降低了学习曲线,因为无需深入了解底层硬件细节。

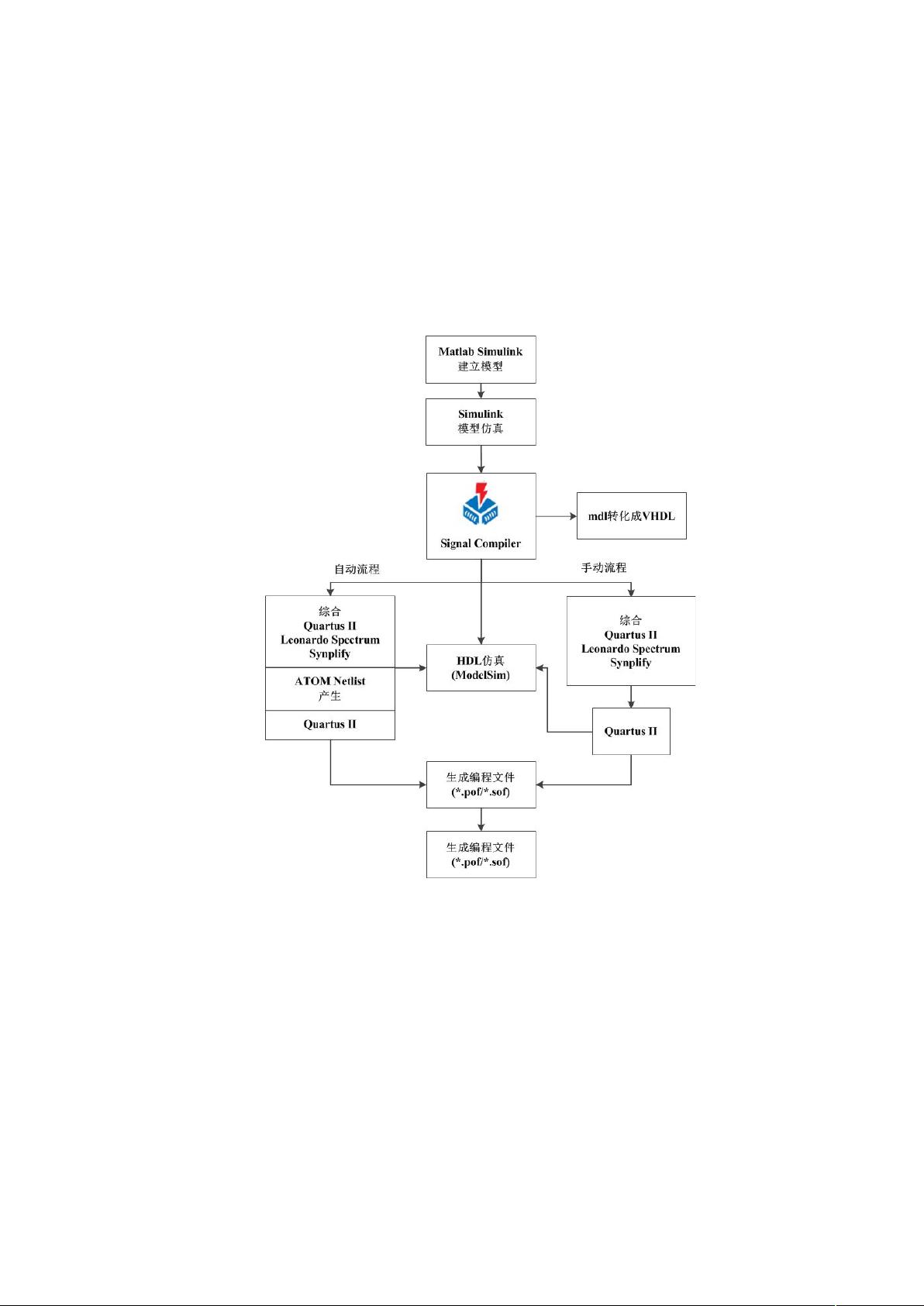

Altera DSP Builder则是另一项关键组件,它整合了MATLAB和Simulink的工具,允许用户在这些强大的数学计算环境中开发和验证数字信号处理算法。这样做的好处在于,设计师可以利用已有的MATLAB库和模型,快速构建和测试算法,然后通过DSP Builder将其高效地映射到FPGA上。

除了VIVADO HLS和DSP Builder,SystemGenerator是NI针对LabVIEW用户的FPGA设计工具,它提供了从图形化界面到硬件加速的桥梁,使LabVIEW开发者能够将他们的算法部署到FPGA中,进一步扩展了FPGA在数字信号处理领域的应用范围。

总结来说,基于FPGA的数字信号处理方法通过结合高级语言和专门设计工具,如VIVADO HLS、DSP Builder和SystemGenerator,显著简化了设计流程,降低了技术门槛,并提高了性能。这对于那些希望利用FPGA性能但不熟悉底层硬件的专业人士来说,是一个极具吸引力的选择。随着HLS技术的发展和成熟,FPGA在数字信号处理领域的地位将进一步提升。

126 浏览量

136 浏览量

点击了解资源详情

2022-06-24 上传

136 浏览量

2022-11-01 上传

268 浏览量

2023-03-02 上传

2022-05-27 上传

gangniu516617

- 粉丝: 0

最新资源

- Saber仿真下的简化Buck环路分析与TDsa扫频

- Spring框架下使用FreeMarker发邮件实例解析

- Cocos2d捕鱼达人路线编辑器开发指南

- 深入解析CSS Flex布局与特性的应用

- 小学生加减法题库自动生成软件介绍

- JS颜色选择器示例:跨浏览器兼容性

- ios-fingerprinter:自动化匹配iOS配置文件与.p12证书

- 掌握移动Web前端高效开发技术要点

- 解决VS中OpenGL程序缺失GL/glut.h文件问题

- 快速掌握POI技术,轻松编辑Excel文件

- 实用ASCII码转换工具:轻松实现数制转换与查询

- Oracle ODBC补丁解决数据源配置问题

- C#集成连接器的开发与应用

- 电子书制作教程:你的文档整理助手

- OpenStack计费监控:使用collectd插件收集统计信息

- 深入理解SQL Server 2008 Reporting Services