VHDL时序电路设计教程:从基础到状态机

需积分: 12 62 浏览量

更新于2024-07-30

收藏 875KB PDF 举报

"VHDL时序电路设计基础,涵盖了VHDL语言在设计时序逻辑电路和状态机中的应用,包括寄存器、计数器、其他时序电路以及状态机的设计方法。课程强调了VHDL中的并行和顺序语句,如并发语句的并发性、顺序语句的执行顺序,以及各种控制结构,如进程、IF语句、CASE语句等。"

在VHDL中,设计时序电路是通过理解和掌握并行和顺序语句的关键。并行语句在VHDL结构体中同时运行,代表电路的不同节点,比如进程(process)、直接信号赋值(<=)、条件信号赋值(when—else)和选择信号赋值(select—when)等。这些并行语句的执行顺序并不影响最终结果,但需要注意的是,条件信号赋值的条件可以不互斥,而选择信号赋值的条件则必须互斥。

相反,顺序语句通常用于进程、函数和子程序中,按照语句顺序依次执行。常见的顺序语句有信号代入(<=)、变量赋值(:=)、IF-ELSIF-ELSE-ENDIF结构、CASE语句、LOOP语句、过程调用(Procedure)以及WAIT和ASSERT语句。其中,IF语句允许选择值可重复或重叠,而CASE语句的选择值必须是互斥的。

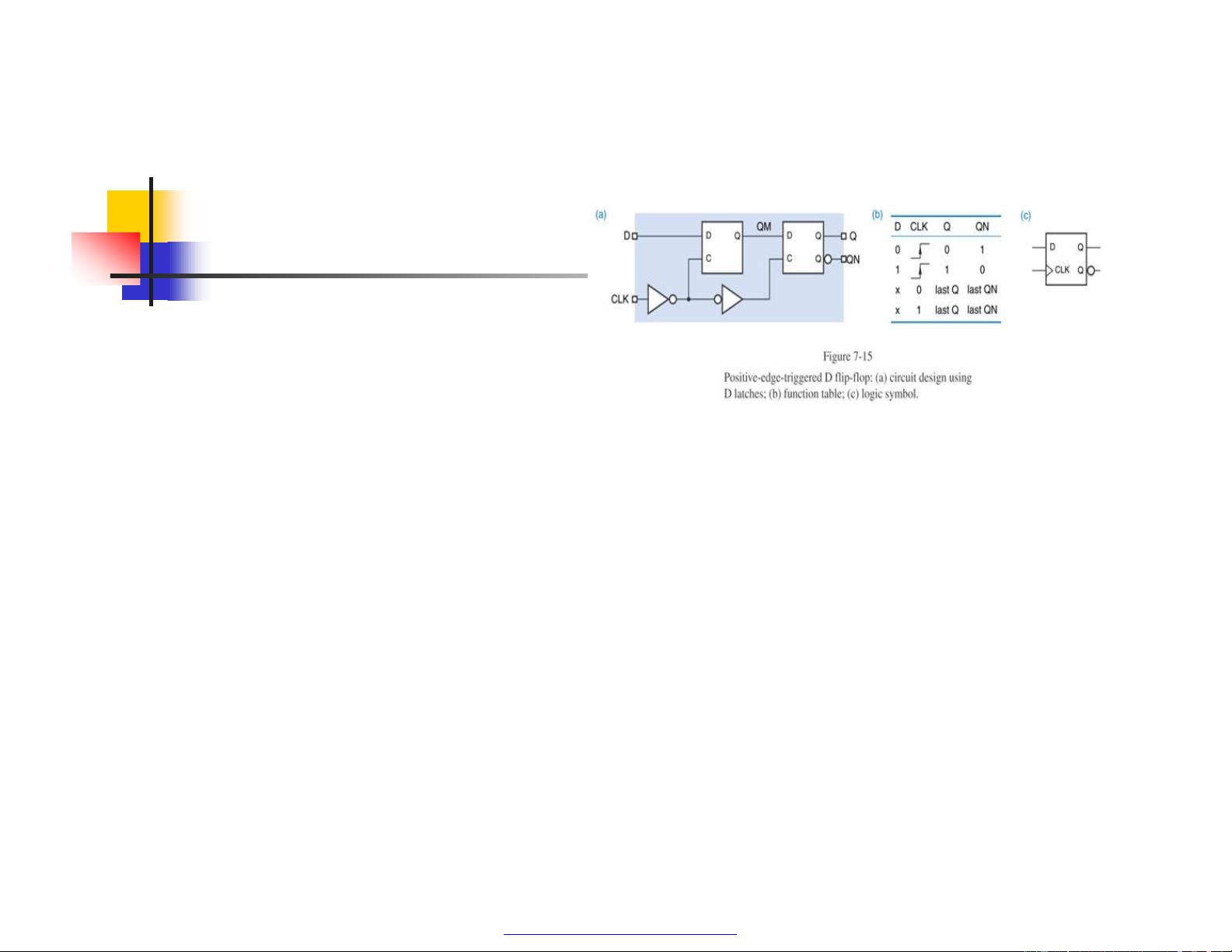

在时序电路设计中,寄存器和计数器是最基本的元素。寄存器用于存储数据,在VHDL中可以通过进程和变量赋值语句实现。计数器则是实现数字系统中计数功能的关键,包括模N计数器、二进制计数器、十进制计数器等,可以通过计数器设计中的递增或递减操作来实现。

此外,状态机设计是时序逻辑电路中的重要部分,用于控制系统的状态转换。它可以是同步状态机或异步状态机,通过CASE语句或者IF-ELSIF-ELSE结构来描述状态间的转移逻辑。状态机的设计能够帮助实现复杂的控制逻辑,如在实时信号处理中,状态机可以确保处理流程的正确性和实时性。

VHDL的这些概念和设计方法对于电子工程和计算机科学领域的学生及从业者来说至关重要,它提供了一种强大的工具来描述和实现数字系统,使得硬件设计变得更加灵活和高效。

378 浏览量

164 浏览量

2009-09-13 上传

368 浏览量

点击了解资源详情

164 浏览量

点击了解资源详情

wesolsot

- 粉丝: 0

- 资源: 4

最新资源

- 易语言36键MIDI电子琴

- bl1nd:我的 Ludum Dare 28 参赛作品的延续

- parallel_ASKI_并行计算_六面体协调网格;_模拟声学;_entirelyht3_网格_

- 简历

- Microsoft-Film-Industry-Analysis:文件,Jupyter笔记本和演示幻灯片,供我们分析有助于电影在熨斗学院取得成功的因素

- Eldinho2.github.io

- 作品答辩扁平化模板论文答辩.ppt.rar

- spree_advanced_cart:对 Spree 更有用的购物车实现

- nativescript-snapkit:使用Snapchat帐户登录到您的应用

- 易语言API录音

- 编程珠玑 第2版(修订版)_编程珠玑修订_资料_

- DataAnalytics

- robot_ws:这是机器人上的主要工作空间

- PeopleLung.fg7wzky7dm.ga4AST6

- svnautobuild-开源

- component-template-issue