AD9522时钟分频芯片在嵌入式系统中的应用解析

需积分: 27 5 浏览量

更新于2024-09-03

收藏 256KB PDF 举报

"嵌入式系统/ARM技术中的浅析AD9522时钟分频电路原理,涉及嵌入式系统设计、时钟分频芯片、AD9522特性、PLL和VCO功能、单片机配置"

在嵌入式系统设计中,时钟管理是一个至关重要的环节,它直接影响着DSP、FPGA等硬件芯片的正常运行。随着系统集成度的提高,单一的晶振源已无法满足多样化的时钟需求,因此,具备灵活分频功能的时钟芯片成为了解决方案的关键。本文以AD9522为例,详细解析了时钟分频电路的原理及其在嵌入式系统中的应用。

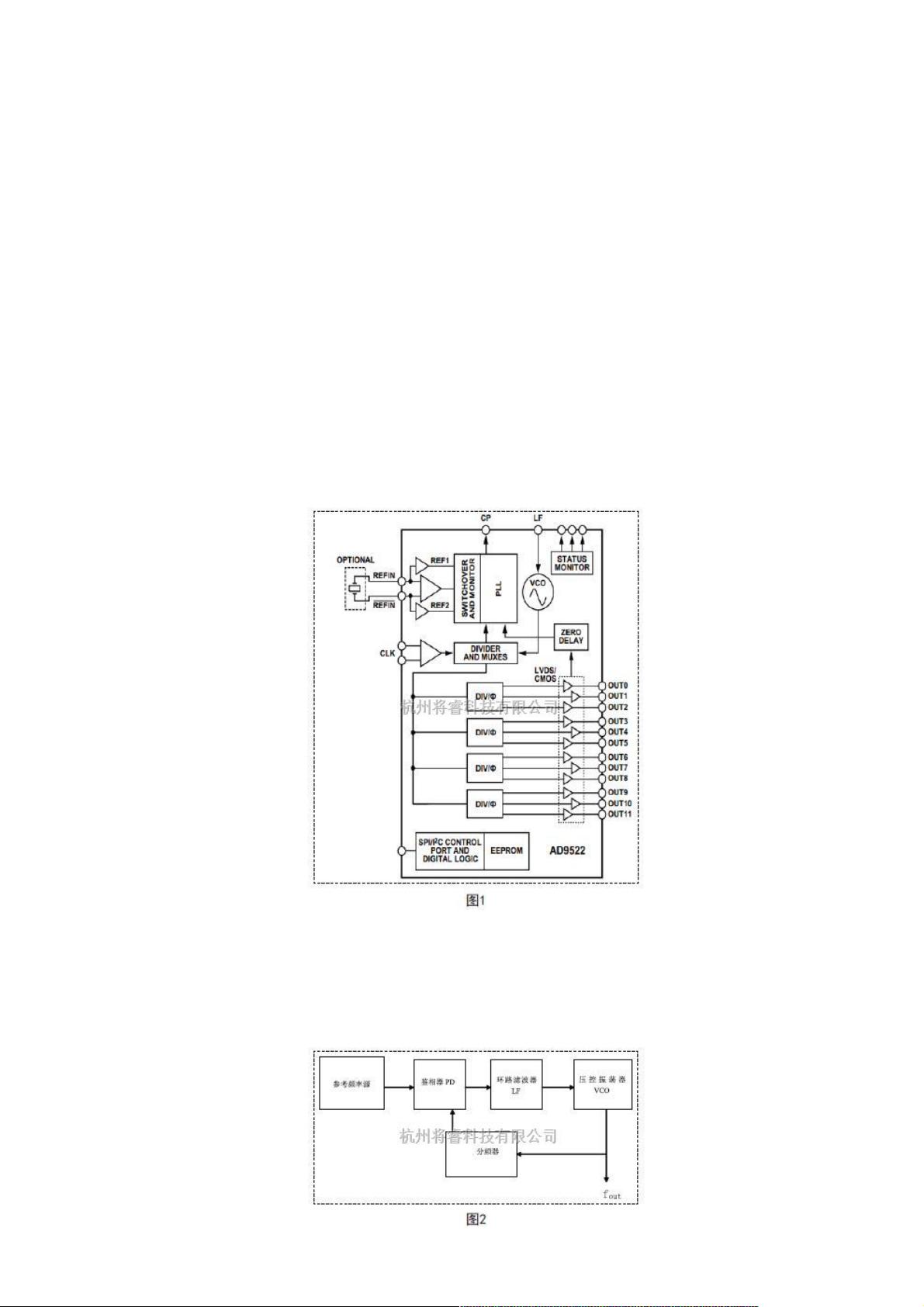

AD9522是一款功能强大的时钟分频芯片,具备多路时钟输出和分配能力,能提供亚皮秒级别的抖动性能,确保高精度的时钟信号。该芯片内置了PLL和VCO,其中VCO的调谐范围从2.02GHz到2.335GHz,提供了广泛的频率选择。AD9522支持SPI和I2C两种通信协议,用户可以通过这些接口对内部的EEPROM进行编程,存储并设置所需的分频寄存器数据。

AD9522有12个LVDS电平输出,分为4组,每组都配备了可配置的分频器,分频比可以在1到32之间自由设定。这样的设计极大地提高了系统的灵活性和可配置性,可以根据实际需求调整时钟频率。

芯片内部的工作原理基于锁相环(PLL)技术。外部输入的晶振信号通过PLL进行倍频或分频处理。VCO产生的信号一部分作为输出,另一部分经过分频后与PLL的参考信号进行相位比较。如果相位出现差异,PLL的电压控制端会调整VCO的频率,以保持两信号的相位一致,实现锁相的目的。这一过程确保了输出时钟信号的稳定性。

在实际应用中,单片机扮演了重要角色,通过SPI或I2C接口对AD9522的寄存器进行配置,以设定所需的分频参数。这种配置方式使得系统能够动态适应不同的工作场景,增强了系统的可移植性和适应性。

AD9522时钟分频芯片在嵌入式系统中扮演了核心角色,它结合了PLL和VCO的高性能特点,提供灵活的时钟管理和分频解决方案。通过单片机的智能配置,可以轻松应对各种复杂的时钟需求,确保系统运行的稳定性和效率。对于嵌入式系统设计者来说,理解并熟练运用这类时钟分频芯片,对于优化系统性能和降低设计复杂度具有重要意义。

2020-12-09 上传

2023-12-05 上传

2023-07-07 上传

2023-05-29 上传

2023-05-12 上传

2023-04-29 上传

2023-06-07 上传

2023-06-05 上传

2023-12-30 上传

weixin_38728360

- 粉丝: 4

- 资源: 926

最新资源

- 李兴华Java基础教程:从入门到精通

- U盘与硬盘启动安装教程:从菜鸟到专家

- C++面试宝典:动态内存管理与继承解析

- C++ STL源码深度解析:专家级剖析与关键技术

- C/C++调用DOS命令实战指南

- 神经网络补偿的多传感器航迹融合技术

- GIS中的大地坐标系与椭球体解析

- 海思Hi3515 H.264编解码处理器用户手册

- Oracle基础练习题与解答

- 谷歌地球3D建筑筛选新流程详解

- CFO与CIO携手:数据管理与企业增值的战略

- Eclipse IDE基础教程:从入门到精通

- Shell脚本专家宝典:全面学习与资源指南

- Tomcat安装指南:附带JDK配置步骤

- NA3003A电子水准仪数据格式解析与转换研究

- 自动化专业英语词汇精华:必备术语集锦