Calibre LVS选项配置指南

需积分: 0 33 浏览量

更新于2024-06-15

5

收藏 2.88MB PDF 举报

"calibre lvs option"

在集成电路设计验证中,Layout Versus Schematic (LVS) 是一个至关重要的步骤,它确保设计的物理布局与电路原理图相匹配。`calibre lvs` 是一款由 Mentor Graphics 提供的业界标准工具,用于执行 LVS 验证。该工具提供了丰富的选项来定制验证过程,以适应不同的设计需求。以下是一些关键的 `calibre lvs` 选项的详细解释:

1. **LVSCHECKPORTNAMES**: 此选项决定是否检查端口名称的一致性。当设置为 `YES` 时,LVS 将验证布局端口和原理图端口的名称是否相同;若设置为 `NO`,则不会进行此检查。

2. **LVSRECOGNIZEGATE**: 用于控制如何识别门级单元。`ALL` 表示识别所有类型的门,`SIMPLE` 只识别简单的门,而 `NONE` 则不识别任何门。

3. **LVSREDUCESPLITGATES**: 如果设为 `YES`,工具会尝试合并分段的门,以简化比较。设为 `NO` 则保持原始布局不变。

4. **LVSABORTONSUPPLYERROR**: 当遇到电源错误时,是否立即停止 LVS 验证。设为 `YES` 表示遇到电源错误即终止,`NO` 则继续执行。

5. **LVSALLCAPACITORPINSSWAPPABLE**: 如果设为 `YES`,允许电容的所有引脚在匹配过程中互换。设为 `NO` 则不允许。

6. **LVSCHECKPORTNAMES**: 与前面的选项类似,但此处未提供建议值或默认值。通常用于检查端口名称是否一致。

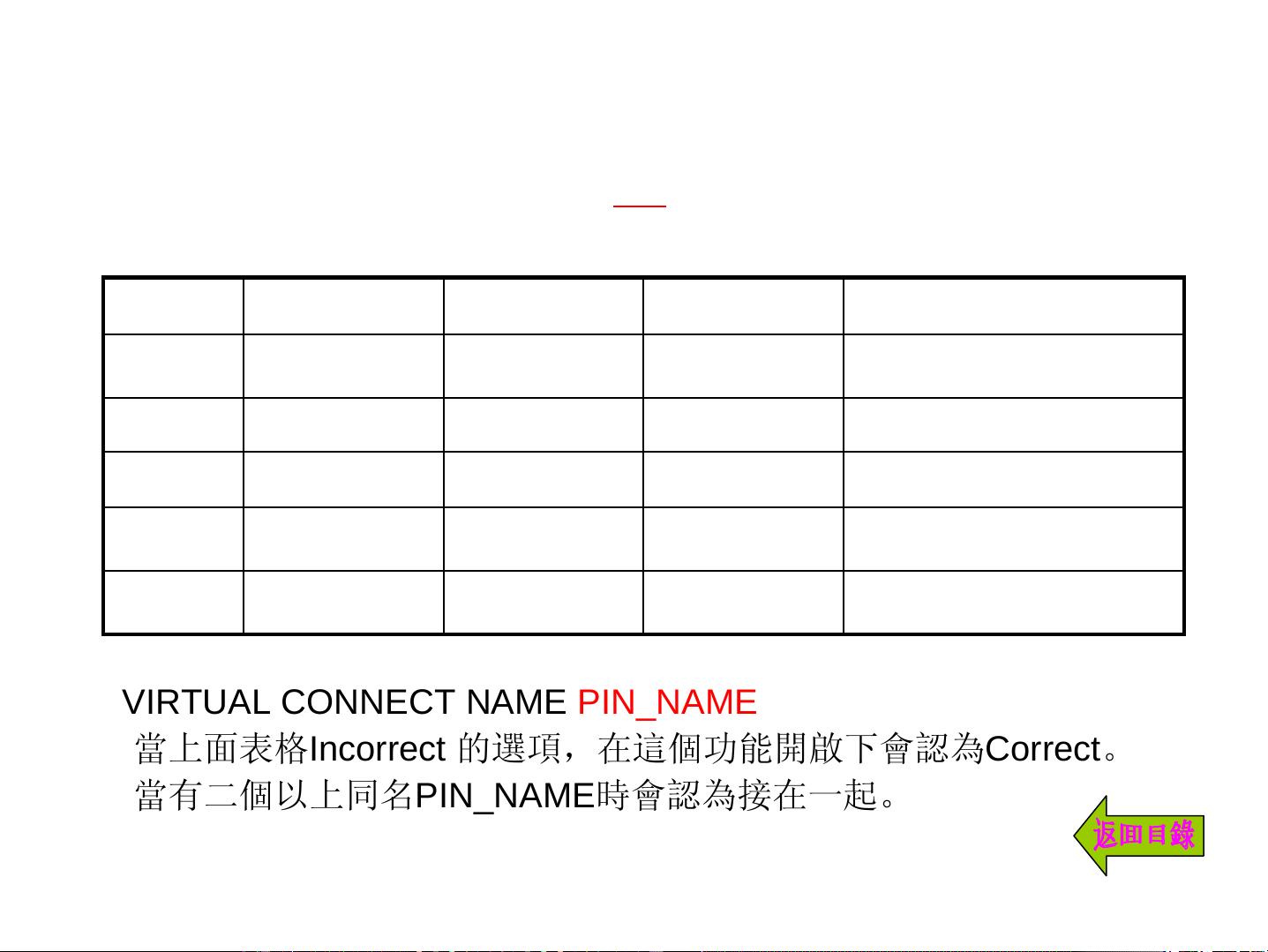

7. **VIRTUALCONNECTCOLON**: 控制虚拟连接的处理方式,`YES` 允许虚拟连接,`NO` 则禁止。

8. **LVSBOX**: 相关选项可能涉及到如何处理布局中的 Box 对象。

9. **LVSCOMPARECASE**: 是否区分文本的大小写。设为 `YES` 会进行大小写敏感的比较,`NO` 则不区分大小写。

10. **LAYOUTDEPTH**、**PORTDEPTH** 和 **TEXTDEPTH**: 这些选项用于指定在不同级别的层次结构中进行 LVS 检查的深度。`ALL` 指所有层次,`PRIMARY` 只检查顶层,`number` 可以指定具体层级。

11. **LVSABORTONSOFTCHK**: 当遇到可容忍的错误(soft check)时,是否停止验证。`YES` 表示停止,`NO` 继续。

12. **LVSSOFTSUBSTRATEPINS**: 选项用于处理衬底引脚,设为 `YES` 表示允许衬底引脚的软匹配,`NO` 则不允许。

13. **LVSFilterUnusedOption** 和 **LVSFilterUnusedBipolar**: 这些选项可能用于过滤掉未使用的元件或双极性元件,以优化验证过程。

14. **LVSGlobalsArePorts**: 设为 `YES` 表示全局信号被视为端口,`NO` 则不视为端口。

15. **TEXTPRINTMAXIMUM**: 控制打印文本的最大数量,`ALL` 表示打印所有文本,`NUMBER` 可限制到指定数量。

16. **LVSPropertyResolutionMaximum**: 设置属性分辨率的最大值,可以指定具体数值或 `All`。

17. **LVSSoftchkPwell_allcontact**: 与软检查相关的选项,可能涉及 Pwell 的处理。

18. **TracePropertyC1C2C3trace_val**: 用于追踪特定属性值的选项。

此外,还有其他一些配置参数,如 `precision1000` 定义了精度,`resolution10` 设定了布局网格尺寸,`LAYOUTPATH` 指定了布局数据库路径,`LAYOUTPRIMARY` 定义了顶层细胞名称,而 `SOURCE` 通常用于指定输入的原理图文件。

通过调整这些选项,设计者可以根据自己的设计规则和需求来优化 LVS 验证过程,确保其高效且准确。理解并正确使用这些选项是进行高质量 LVS 验证的关键。

2013-03-08 上传

103 浏览量

点击了解资源详情

2023-02-03 上传

2017-04-17 上传

177 浏览量

2012-03-06 上传

点击了解资源详情

点击了解资源详情

榴莲纤层

- 粉丝: 38

- 资源: 3

最新资源

- 高清艺术文字图标资源,PNG和ICO格式免费下载

- mui框架HTML5应用界面组件使用示例教程

- Vue.js开发利器:chrome-vue-devtools插件解析

- 掌握ElectronBrowserJS:打造跨平台电子应用

- 前端导师教程:构建与部署社交证明页面

- Java多线程与线程安全在断点续传中的实现

- 免Root一键卸载安卓预装应用教程

- 易语言实现高级表格滚动条完美控制技巧

- 超声波测距尺的源码实现

- 数据可视化与交互:构建易用的数据界面

- 实现Discourse外聘回复自动标记的简易插件

- 链表的头插法与尾插法实现及长度计算

- Playwright与Typescript及Mocha集成:自动化UI测试实践指南

- 128x128像素线性工具图标下载集合

- 易语言安装包程序增强版:智能导入与重复库过滤

- 利用AJAX与Spotify API在Google地图中探索世界音乐排行榜