VHDL实现数字秒表:EDA课设详解

"EDA课程设计项目——基于VHDL的数字秒表设计"

在本EDA课程设计中,主要目标是构建一个数字秒表,它由多个分模块组成,包括显示译码器、分频器、十进制计数器、六进制计数器以及报警器。设计的关键在于实现精确的计时脉冲和有效的数据处理,以确保秒表功能的准确性和可靠性。

首先,秒表的逻辑结构由几个关键部分构成。显示译码器负责将内部的BCD码转换为适合显示的格式,以便在数码管上清晰地呈现时间。分频器是系统的心脏,其主要任务是生成稳定的100Hz计时脉冲,这使得秒表能够从百分之一秒开始计数。分频器通常需要从较高频率的时钟源(如2.5MHz)进行分频,以达到所需的精度。

设计中包含两个分频器。分频器1生成100Hz的时钟,而分频器2则产生更频繁的脉冲,用于驱动时间扫描模块的扫描脉冲,确保数码管上的时间显示能够正确滚动。接下来,四个10进制计数器分别用于计数百分之一秒、十分之一秒、秒和分钟,而两个六进制计数器则处理十秒和十分位。所有这些计数器的输出都是BCD码,以便与显示译码器无缝对接。

时间扫描模块是设计中的另一个重要组件,它的职责是控制数码管上显示的时间段,确保在不同时间单位之间正确切换。显示译码器接收来自计数器的BCD码,并将其转换为对应数码管的段码,从而实现时间的可视化。

报警器控制模块在秒表达到特定时间(例如60分钟)时触发蜂鸣器报警,提醒用户时间已到。这一功能通过检测计数器状态来实现,当达到预设阈值时,会向报警器发送信号使其发声。

整个设计遵循层次化方法,将任务分解为七个子模块,每个模块都有明确的功能定义和接口规定。然后,这些子模块被整合到顶层文件中,进行联试仿真和下载,以验证整个系统的功能和性能。

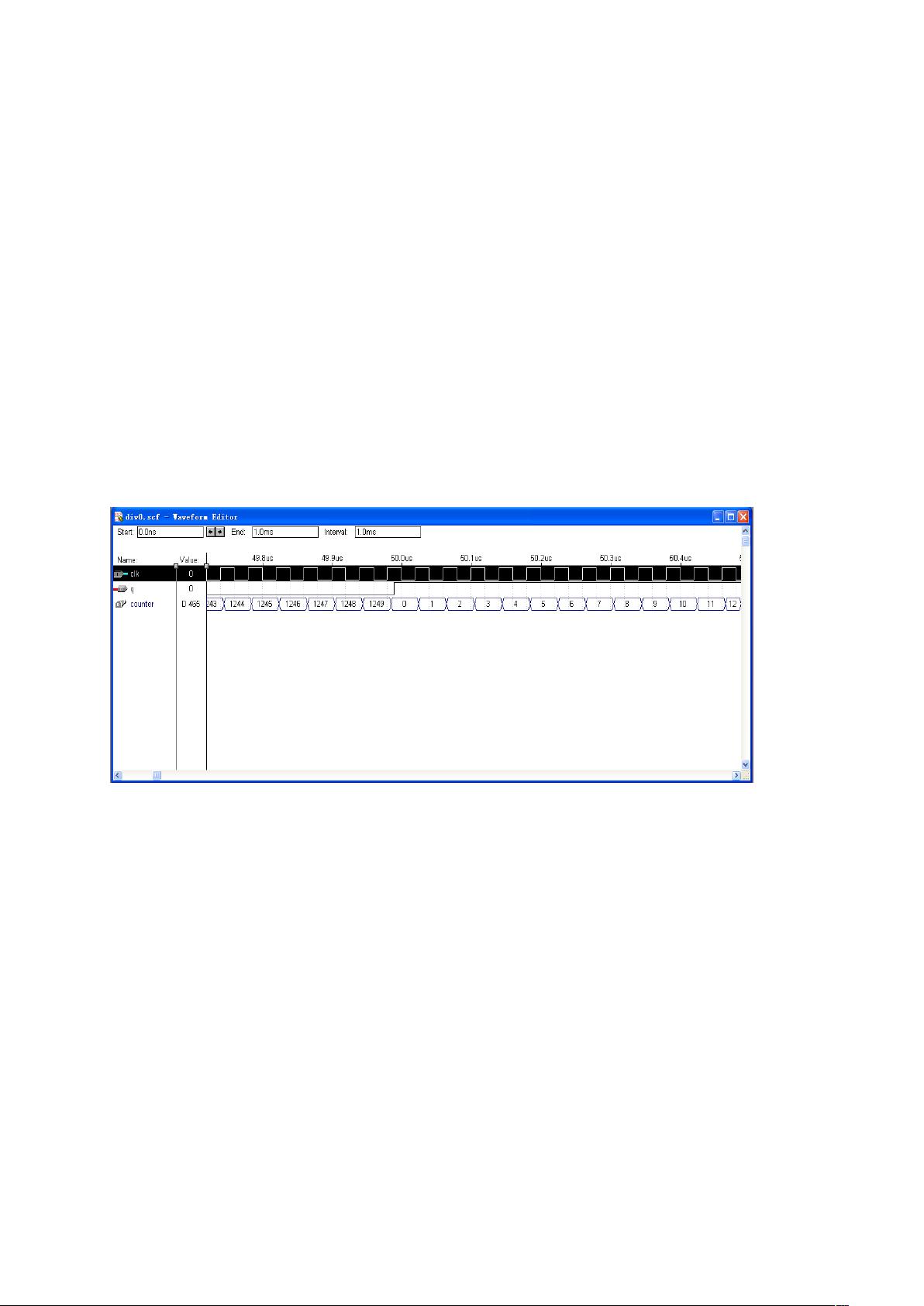

具体到VHDL代码实现,例如分频器1的代码片段展示了如何利用进程(process)来处理时钟边沿,计数器变量(counter)用于存储当前计数值,当计数值达到设定阈值(12499)时,计数器复位并翻转输出信号(q)。这是通过条件语句和时钟边沿检测实现的。

总结来说,这个EDA课程设计项目通过VHDL编程语言,结合了数字逻辑设计原理,实现了从时钟源分频、计数、译码到显示报警的完整数字秒表功能,为学习者提供了实践数字系统设计的宝贵案例。

相关推荐

mofeng129

- 粉丝: 0

最新资源

- DWR实战:Ajax框架与Ext集成教程

- Oracle使用常见问题与解答集锦

- ECSide在Web项目的应用与优势

- 提升XP系统性能:优化技巧与设置建议

- 经典面试题集锦:46家公司笔试难题解析

- PHP动态网页制作入门与发展历程

- jQuery中文入门教程:从零开始掌握

- 全面元器件封装查询指南:附带封装图

- Linux系统管理与高级编程实战指南

- Linux系统编程实战:外壳脚本与高级技术详解

- Linux系统网络功能深度解析:TCP/IP、IPv6与更多

- Linux系统深度解析与高级编程实战指南

- Linux系统详解:编程与高级技术

- Windows/Linux/Unix系统中MAC地址查询与配置详解

- 掌握C51单片机基础与8051工程开发指南

- Flex事件流详解:机制与事件绑定