SOC微体系结构:存储器设计详解

版权申诉

3 浏览量

更新于2024-06-18

收藏 2.32MB PPT 举报

“SOC微体系结构设计第五讲 存储器设计.ppt”

这篇课件主要讲述了微体系结构设计中的存储器设计,涵盖了随机存取存储器(RAM)、只读存储器(ROM)、双端口RAM、先进先出(FIFO)存储器以及CRC校验电路设计等多个方面。以下是详细的解释:

1. **随机存取存储器(RAM)设计**:

- RAM分为静态RAM (SRAM) 和动态RAM (DRAM)。SRAM速度快但功耗大,适合做CPU缓存;DRAM则功耗低但速度相对较慢,常用于系统主内存。

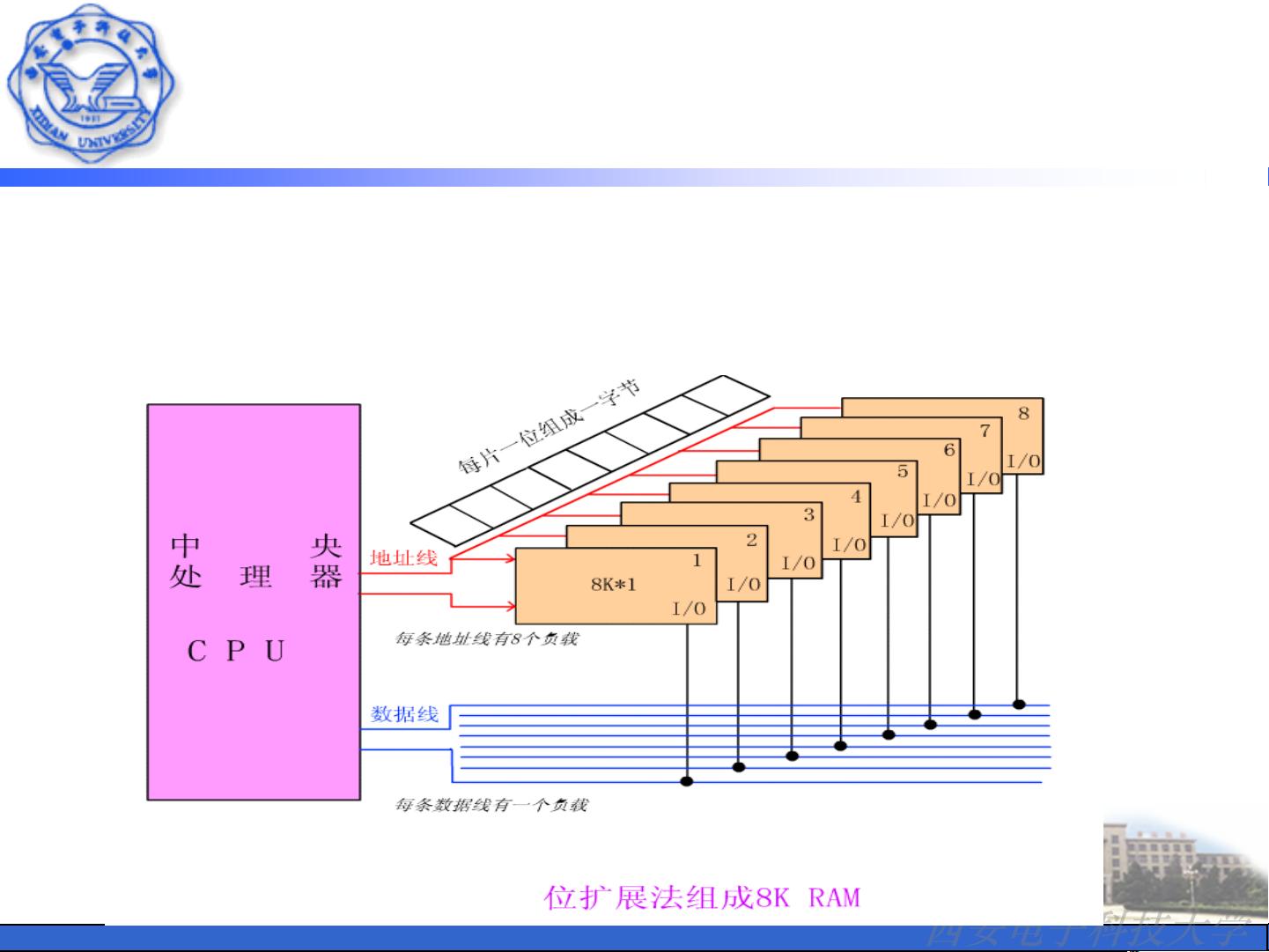

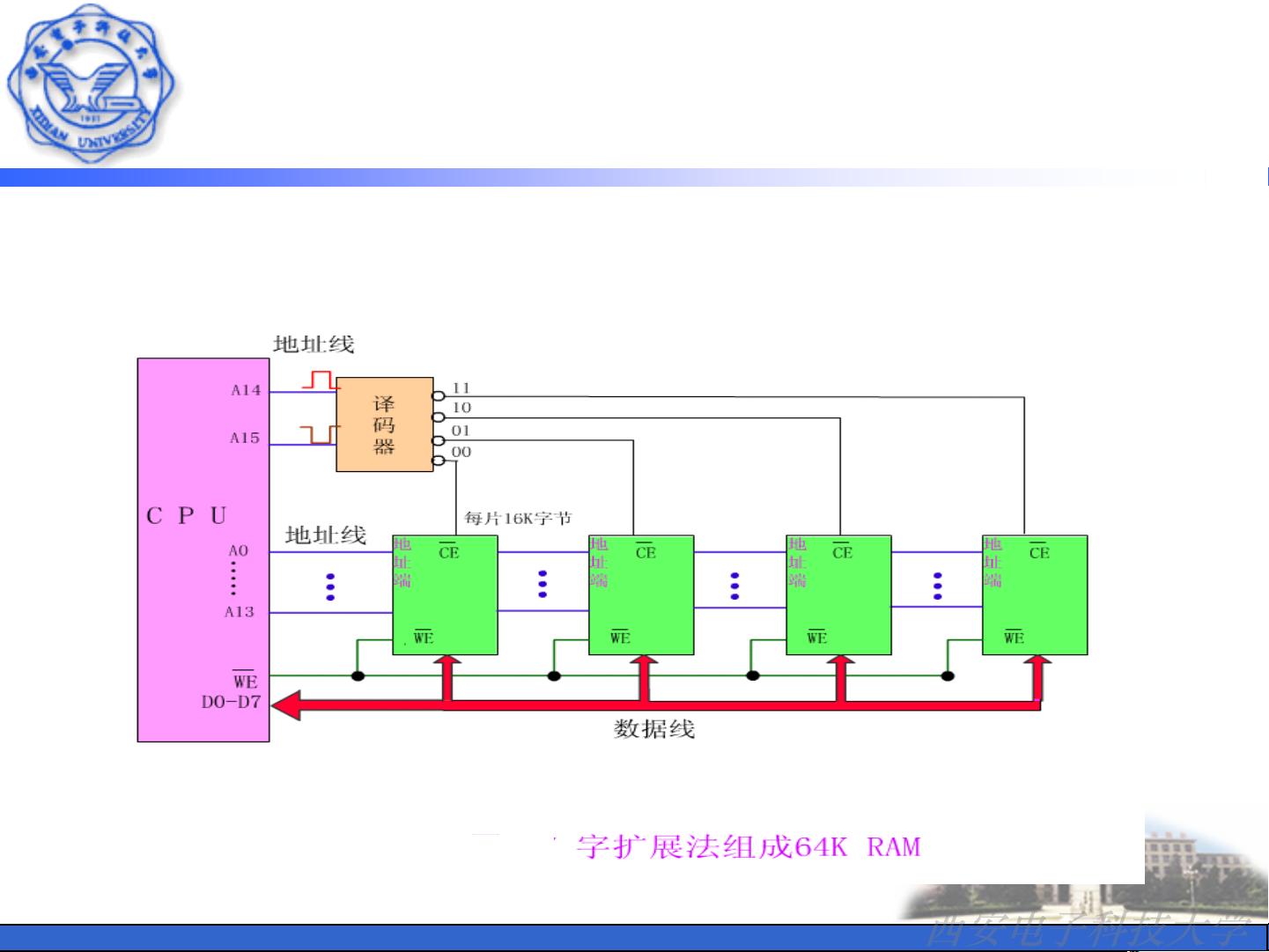

- 地址译码是RAM的重要组成部分,包括一维和二维译码方式。一维译码适用于小容量存储器,而二维译码在大容量存储器中更常见,它通过行地址和列地址来确定具体存储单元。

2. **只读存储器(ROM)设计**:

- ROM包含掩模ROM、PROM、EPROM、E2PROM和Flash等类型。掩模ROM在制造时即被编程,内容不可更改;PROM、EPROM、E2PROM和Flash则是可编程或可擦写的,其中Flash在现代电子设备中广泛应用。

3. **双端口RAM设计**:

- 双端口RAM允许数据同时从两个独立的端口读写,适用于需要并发访问数据的场合。

4. **先进先出(FIFO)设计**:

- FIFO是一种特殊的存储结构,数据按照先进入的顺序先出去,常用于数据缓冲和串行通信接口。

5. **CRC校验电路设计**:

- CRC(Cyclic Redundancy Check)是一种广泛用于数据传输错误检测的校验方法,通过计算数据的校验和来检测传输过程中可能出现的错误。

6. **设计方法**:

- 模块的功能和原理分析、结构与电路模型的建立、使用VHDL语言进行设计实现,以及通过FPGA进行硬件验证是存储器设计的基本步骤。

7. **SRAM(6264芯片)的读写时序**:

- 读时序中,地址和片选信号加载后,OE(输出使能)信号变为低电平,允许数据读出,而WE(写使能)保持高电平。

- 写时序中,数据加载到数据总线上,同时WE变为低电平,将数据写入指定地址。

以上内容详尽地阐述了存储器设计的基础知识,对于理解微体系结构中存储器的工作原理及其设计方法具有重要意义。

2024-01-01 上传

2024-01-01 上传

2024-01-01 上传

2021-10-02 上传

2022-06-28 上传

2021-09-21 上传

我慢慢地也过来了

- 粉丝: 1w+

- 资源: 4084

最新资源

- Simple Simon Game in JavaScript Free Source Code.zip

- 西门子工控软件PCS7电子学习解决方案.rar

- wc-marquee:具有派对模式的香草Web组件字幕横幅

- ansible-configurations:ansible配置

- 2,UCOS学习资料.rar

- Mancala Online-开源

- irddvpgp.zip_电机 振动

- aiopg:aiopg是用于从asyncio访问PostgreSQL数据库的库

- fist_springboot:第一个构建的springboot项目

- DataGo:这是我的数据科学页面

- WPE Pro 0.9a 中文版

- 西门子结构化编程.rar

- opaline-theme:VSCode的颜色主题

- simulink_SimMechanicS.zip_MATLAB s-function_simulink机械臂_机械臂 pd控制

- Auto Lotro Launcher-开源

- Simple Math Application