Allegro16.6约束规则详解:从基础到高级设置

需积分: 12 57 浏览量

更新于2024-07-14

收藏 7.5MB PDF 举报

本文是一份关于Allegro 16.6约束规则设置的详细指南,涵盖了CADence Allegro电路设计软件中的关键功能。以下是主要内容概要:

1. **线间距设置**:

- 设置默认间距规则:通过约束管理器,用户可以修改 DEFAULT 规则的间距值,以适应设计需求。

- 定义特殊间距约束:允许创建自定义间距规则,如为特定网络分配特定间距,如12mil。

2. **线宽设置**:虽然未在部分内容中明确提及,但理解线宽设置同样重要,可能涉及设置导体宽度以满足信号完整性要求。

3. **过孔设置**:在规则设置中,过孔的配置是实现电路板互连的关键步骤,可能包括过孔大小、位置和数量限制。

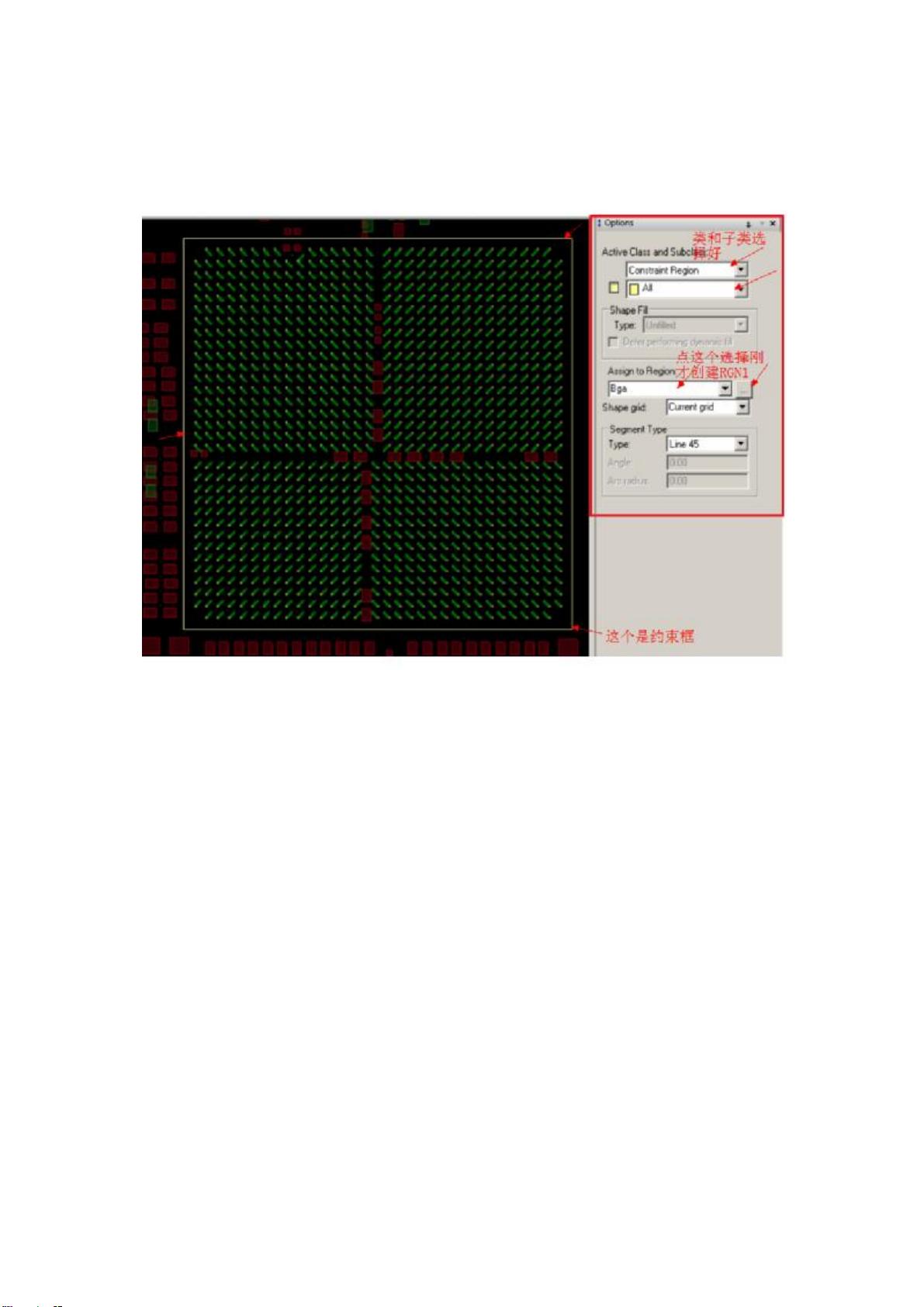

4. **区域约束规则**:用于组织和优化设计布局,例如,可能有针对不同功能区的特定规则。

5. **阻抗设置**:确保信号在布线过程中维持合适的阻抗,这对于高速信号的传输至关重要。

6. **走线长度范围和等长**:

- 不过电阻的NET等长:网络之间的等长规则,保持信号传输速度一致。

- 过电阻的XNET等长:当线路经过电阻时,对网络长度的处理规则。

- T型等长:处理T形连接线的长度控制。

7. **通用属性设置**:包括封装、层叠和材料属性,有助于电路板制造过程中的准确性和一致性。

8. **差分规则设置**:

- 创建差分对:设置差分信号对的规则,如信号对的间距和方向。

- 差分约束设置:确保差分对的特性符合设计规格。

9. **Pin Delay**:针对引脚延迟进行约束,保证信号到达引脚的时间满足设计要求。

10. **高级约束规则设置**:

- 单个网络长度约束:为特定网络设置长度上限或下限。

- 类别(a+b)和类别(a+b-c)长度约束:根据信号类型和优先级的不同,设置多级的长度控制。

- 延迟约束的应用:结合传播延迟考虑整体设计性能。

文章提供了一个全面的框架,让读者能够系统地理解和操作Allegro 16.6中的约束规则,以实现高效、精确的电路板设计。对于电子设计工程师来说,这份指南是提升设计质量和效率的重要参考资料。

1026 浏览量

247 浏览量

2798 浏览量

1833 浏览量

3793 浏览量

309 浏览量

1102 浏览量

124 浏览量

点击了解资源详情

Y.Tao

- 粉丝: 51

- 资源: 8

最新资源

- ID3算法C语言编写的源程序

- Web Service开发指南

- 基于MC9S12DP256 的电动助力转

- 磁盘阵列详细概述让你彻底明白RAID的各种级别

- 基于DM642的图像处理系统设计及应用.pdf

- QNX安装说明手册。QNX的开发使用

- 2008三级网络技术上机(南开100题)

- 原汁原味的 C# Language Specification 1.2

- siebel工作流管理指南

- JMS简明教程 详细的讲解JMS

- ActiveMQ教程

- WebSphere Service Registry and Repository Handbook

- ORACLE入门心得

- iPhoneAppProgrammingGuide.pdf

- 计算机网络 作业 宝德学院

- tomcat数据源,非常全面.doc