Vivado设计套件HLS中文修订教程

“ug871(中文翻译修订版).pdf”是一个关于Xilinx Vivado设计套件中高层次综合(High-Level Synthesis, HLS)的教程文档,特别针对UG871的2021.1版本进行了中文修订。该文档旨在帮助那些英语不太熟练的读者更好地理解和使用HLS进行FPGA设计。

本教程详细介绍了使用HLS将C、C++和SystemC代码转化为硬件描述语言(RTL,如Verilog或VHDL)实现的过程。它分为多个章节,逐步引导读者了解和掌握HLS的基本概念和实践技巧:

1. **教程概述**:这一部分为读者提供了整个教程的总体介绍,包括HLS如何将高级编程语言的代码转化为适合FPGA的RTL代码,以及如何通过优化指令来改善设计的面积和性能。

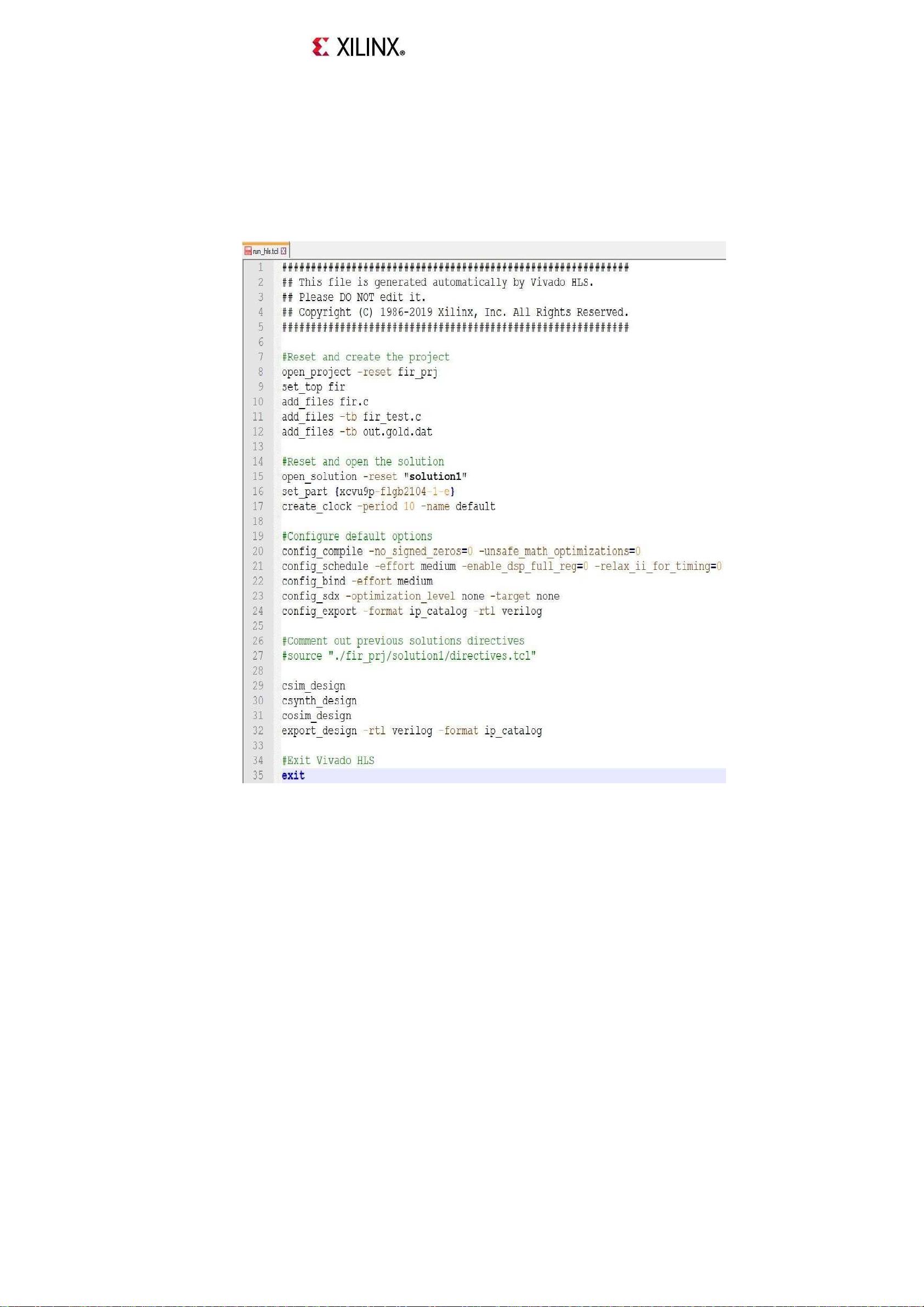

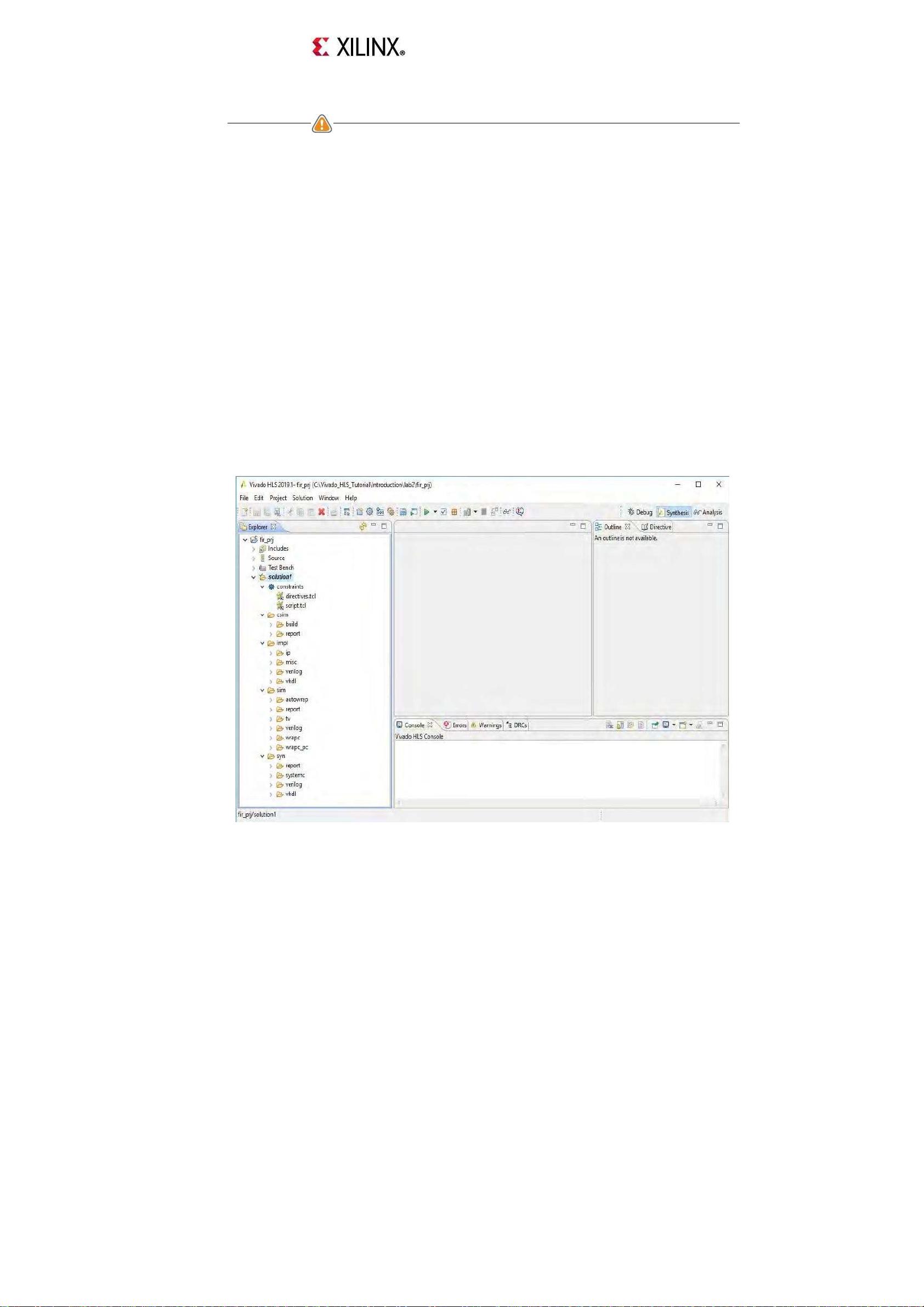

2. **高层次综合介绍**:本章深入介绍了HLS工具及其工作原理,让读者理解如何通过图形用户界面(GUI)与HLS交互,以及如何设置和配置HLS项目。

3. **C验证**:这部分讲解了如何使用C代码进行功能验证,确保软件模型与预期行为一致,这是HLS流程的关键步骤。

4. **接口综合**:介绍如何处理C代码中的输入输出接口,使其适应硬件实现,并讨论不同类型的接口,如AXI4等。

5. **任意精度类型**:讲解HLS如何处理浮点运算和自定义数据类型,这对于实现精确计算和高效硬件设计至关重要。

6. **设计分析**:本章涵盖了设计性能分析工具,如报告和图表,帮助用户评估和优化设计的性能、面积和功耗。

7. **设计优化**:详细阐述了如何使用HLS的指令和选项来优化设计,包括循环展开、并行化、流水线等技术。

8. **RTL验证**:介绍如何在RTL级别验证HLS生成的代码,确保其正确性和可靠性。

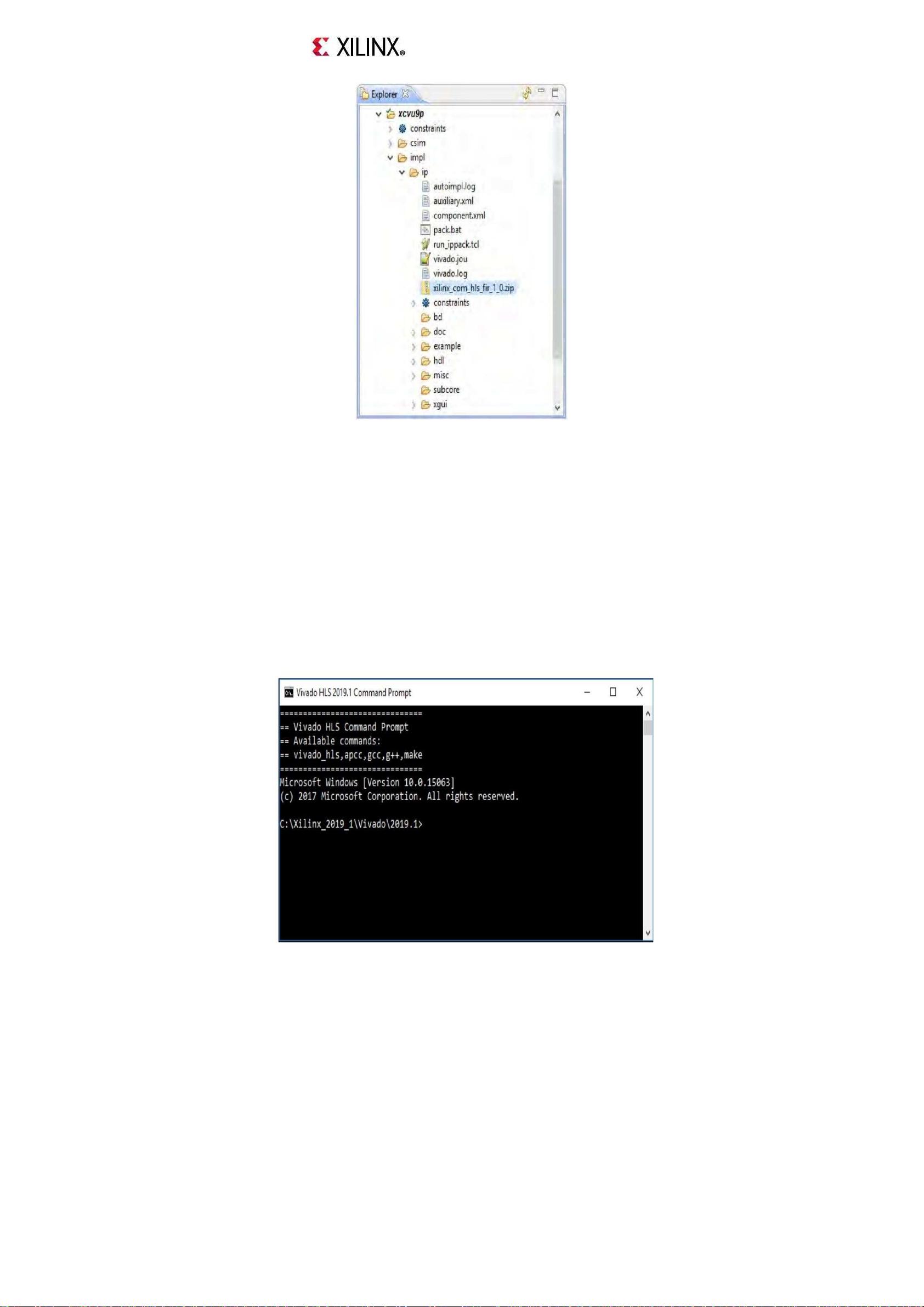

9. **在IP集成器中使用HLS IP**:讲解如何将HLS产生的IP核集成到更大的Xilinx IP生态系统中,以及如何在Vivado的IP Integrator工具中使用它们。

10. **在Zynq SoC设计中使用HLS IP**:专门针对Zynq系列SoC,探讨如何将HLS IP与处理器系统协同工作。

11. **在DSP系统生成器中使用HLS IP**:展示了如何在Xilinx的DSP系统设计中利用HLS的功能。

12. **附录**:包含额外的资源链接和法律通知,为读者提供更全面的支持信息。

这个修订版文档通过修正机器翻译的错误,确保了内容准确无误,对初学者来说是一个很好的HLS学习资源,能够帮助他们快速上手并深入理解高层次综合在FPGA设计中的应用。

2020-01-16 上传

2024-04-15 上传

点击了解资源详情

点击了解资源详情

2019-07-30 上传

2023-04-23 上传

2021-08-09 上传