FPGA时序约束技术详解

需积分: 11 114 浏览量

更新于2024-07-17

收藏 2.03MB PDF 举报

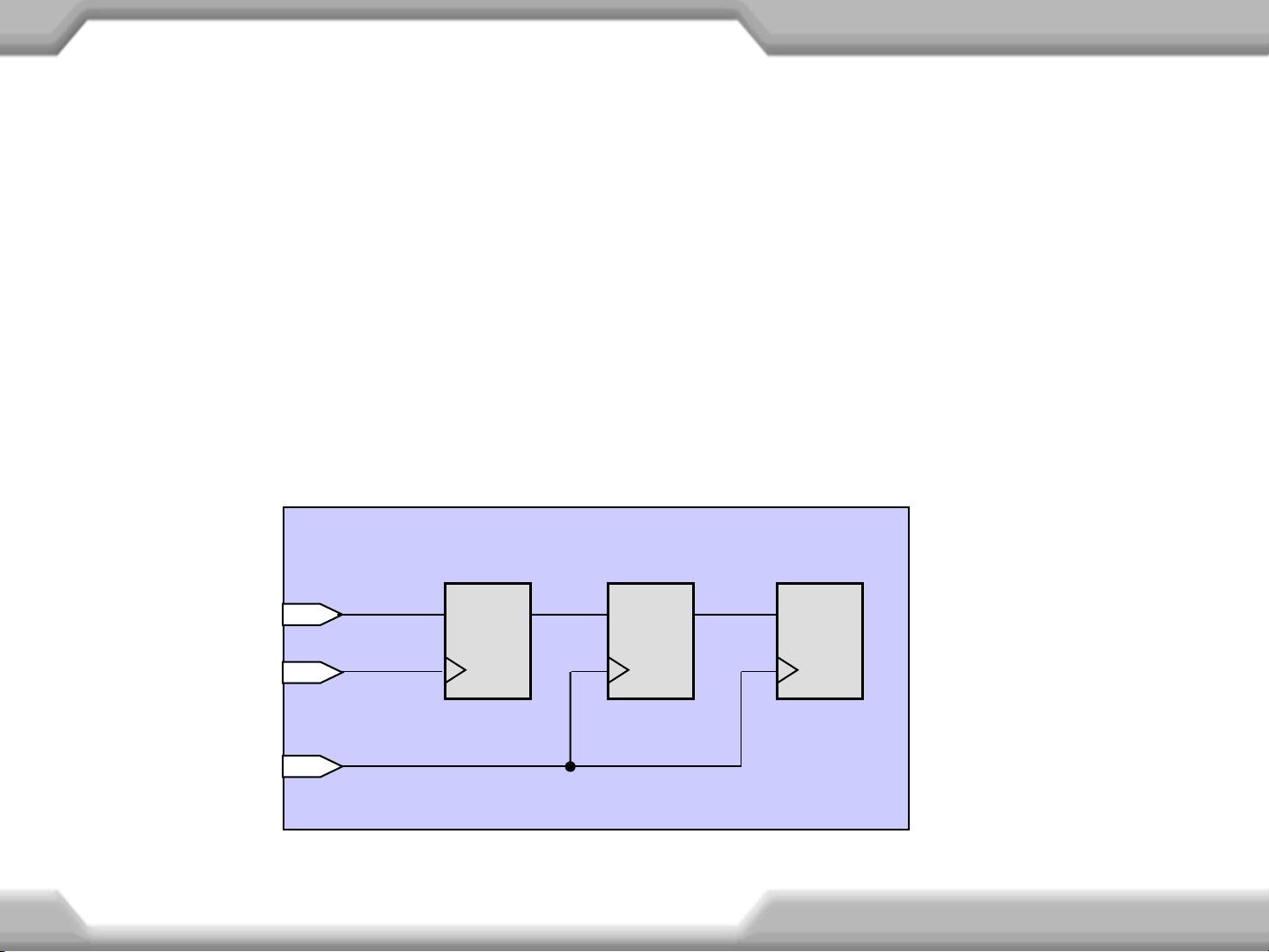

"该资源主要介绍了FPGA时序约束的方法,包括其目的、内容、针对Xilinx和Altera FPGA的约束方法以及时序约束的基本原则。时序约束对于优化FPGA设计性能至关重要,尤其是在高频率和复杂设计中。它帮助规范设计的时序行为,指导综合和布局布线,确保设计满足预设的时序条件。同时,时序约束还用于提高设计的工作频率,提供正确的时序分析报告,并指定FPGA引脚的位置和电气标准。"

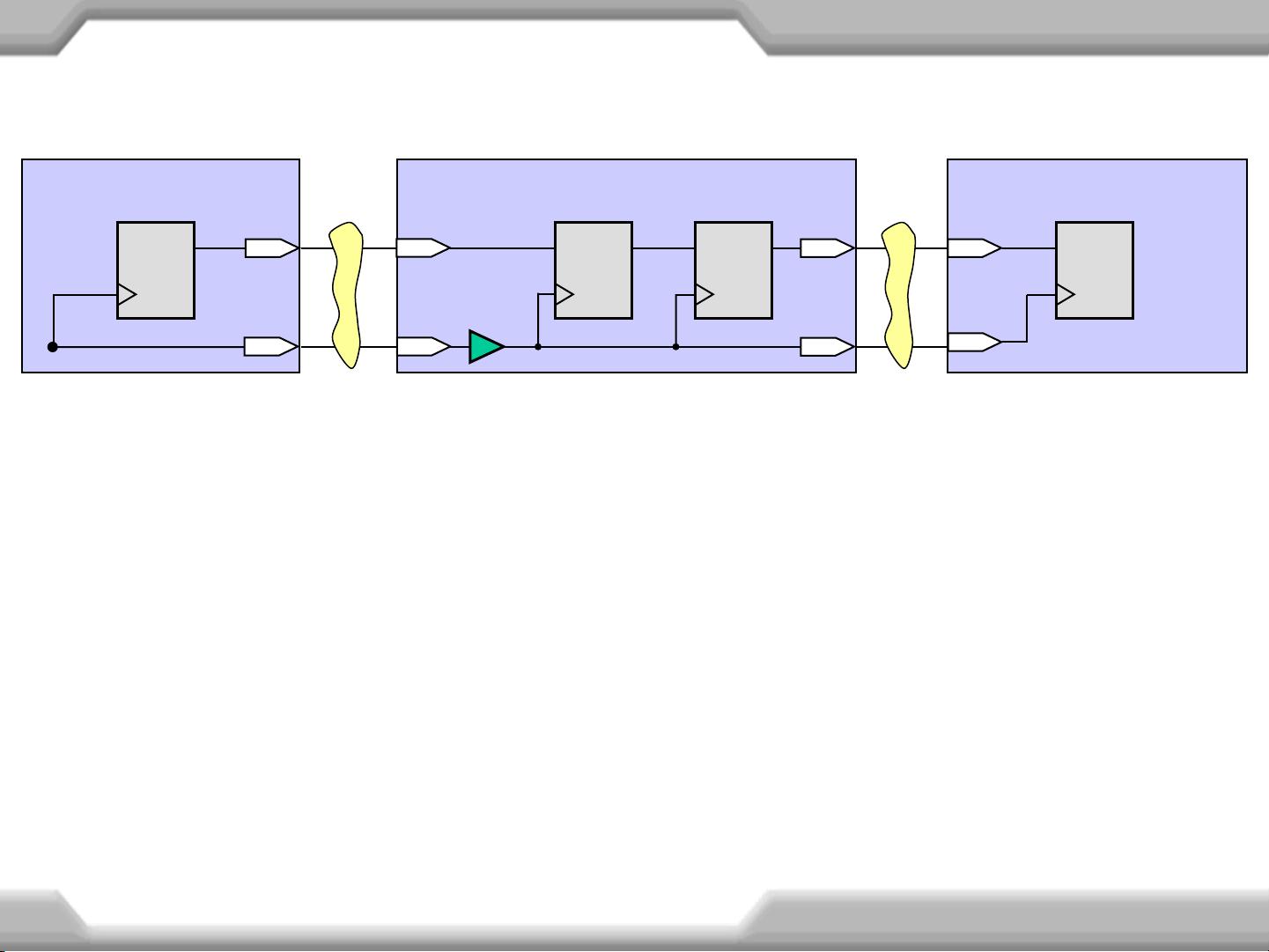

在FPGA设计中,时序约束是不可或缺的一部分,它旨在明确设计者的性能期望,以便于综合、映射、布局和布线工具能够按照这些要求进行操作。时序约束的目的是为了确保设计能够在给定的时间内正确执行,这对于高速和复杂的设计尤其重要。设计工具并不能自动找到最佳的布局和布线方式以达到最高的运行速度,因此需要通过时序约束来设定性能目标。

Xilinx FPGA的时序约束通常涉及Xilinx的时序约束语言,如UCF (User Constraints File) 或 XDC (Xilinx Design Constraints) 文件,其中包含了关于时钟路径、数据路径和I/O约束的具体信息。同样,Altera FPGA的时序约束则通常使用QSF (Quartus Settings File) 或 SDC (Synopsys Design Constraints) 文件来定义。

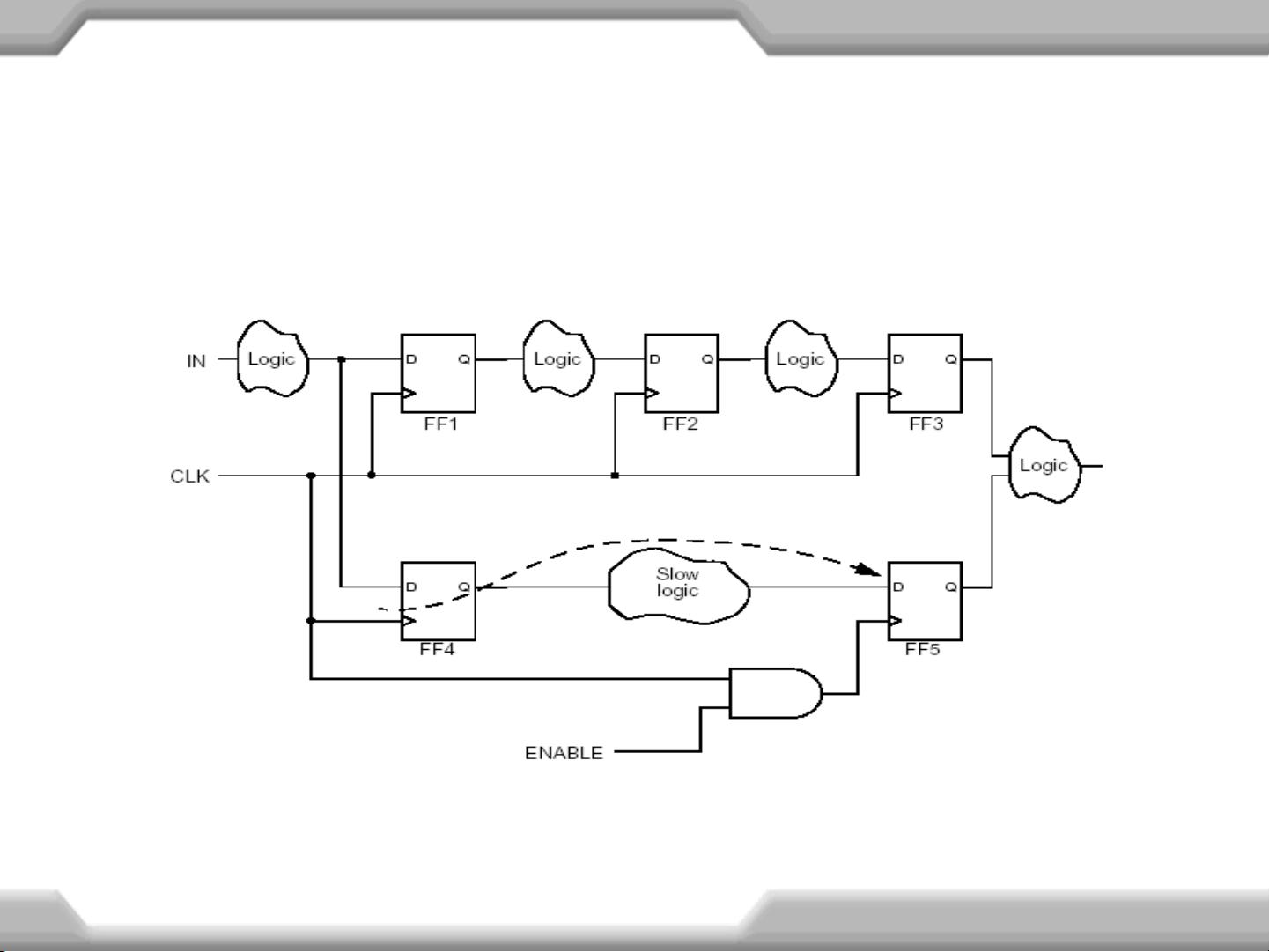

时序约束的内容包括但不限于:

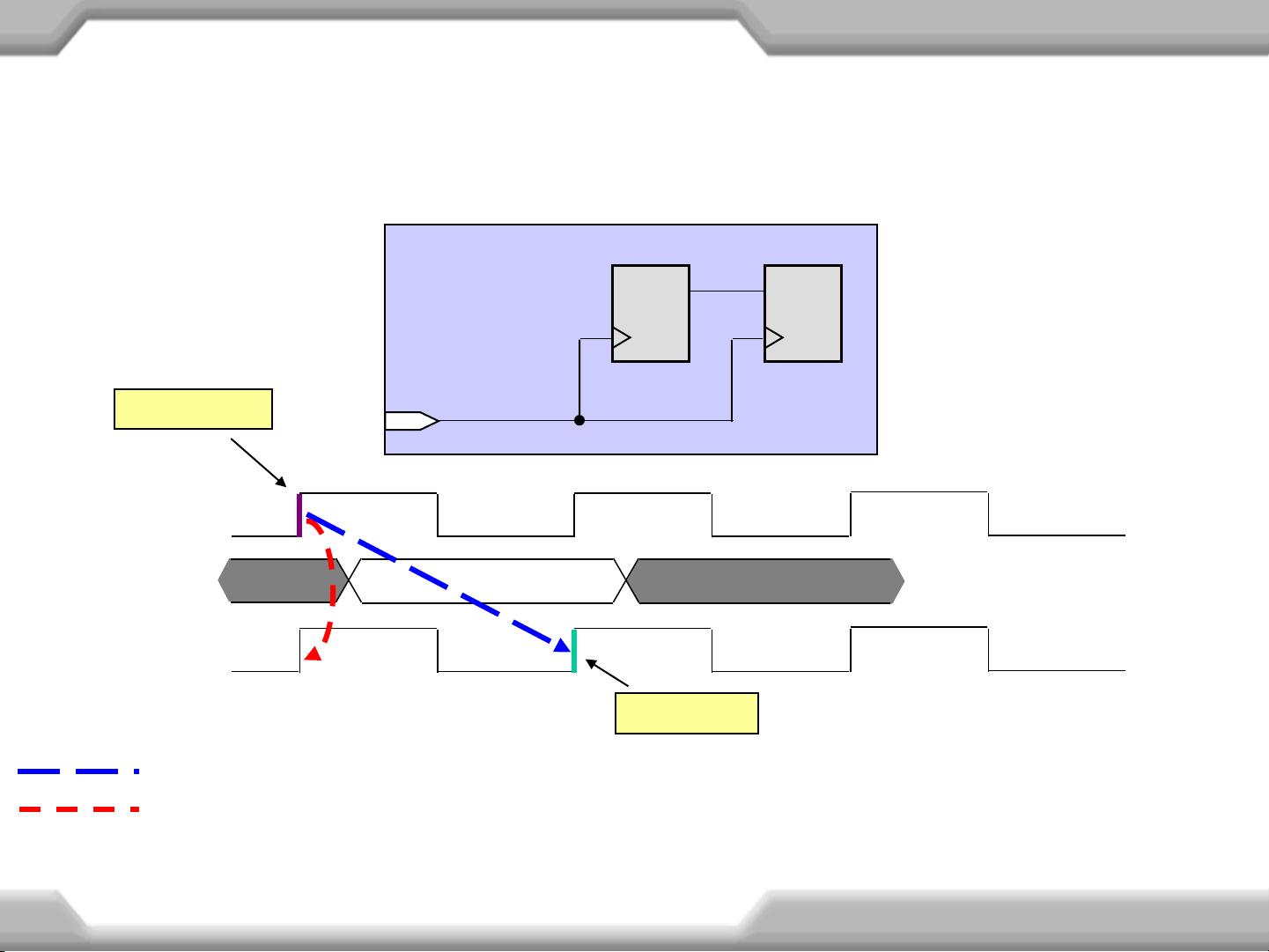

1. **时钟约束**:定义时钟网络,包括时钟源、时钟路径和时钟域之间的关系,以确保时钟同步。

2. **数据路径约束**:规定数据在特定路径上的延迟要求,用于确保满足建立时间和保持时间。

3. **I/O约束**:指定输入/输出引脚的位置、速度等级和接口标准,以适应外部设备。

4. **功耗和面积约束**:有时也会设定这些约束以优化设计的功耗和物理占用空间。

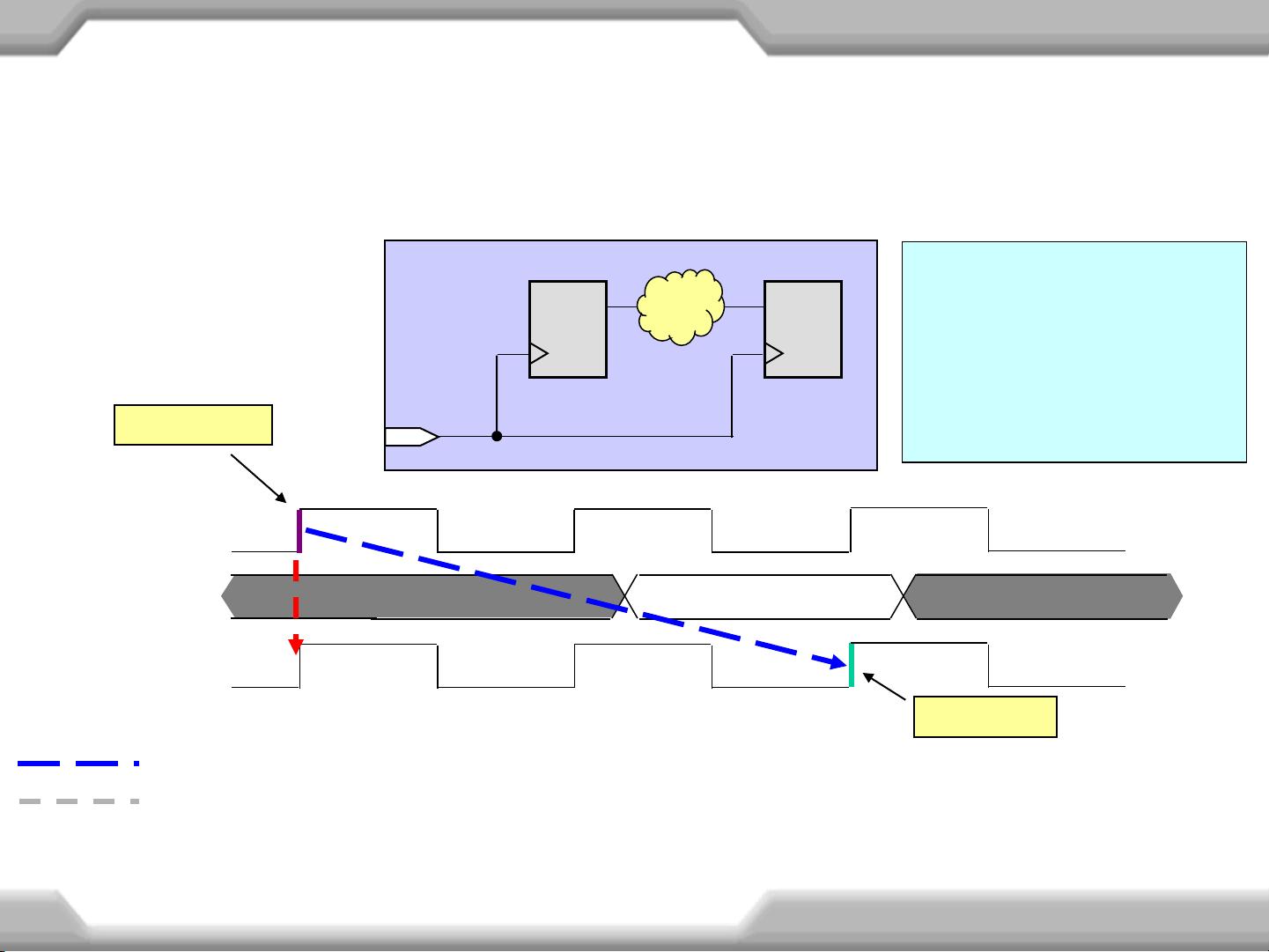

在实施时序约束时,有几个重要的原则需要遵循:

- 约束应合理且实际可行,过紧的约束可能导致编译时间过长,而不合理的约束可能使工具无法完成任务。

- 应使用时序分析报告来验证约束的合理性,并在设计实现后检查静态时序报告,以确认是否达到了性能目标。

- 如果时序约束未满足,应根据时序报告分析问题所在并进行调整。

时序约束对于提升FPGA设计的效率和性能具有决定性的作用,它是实现高性能FPGA设计的关键步骤。通过对设计进行精确的时序约束,设计者可以有效地缩短逻辑和布线延时,从而提高工作频率,确保设计的正确性和可靠性。

377 浏览量

190 浏览量

296 浏览量

349 浏览量

442 浏览量

159 浏览量

163 浏览量

fcc2008

- 粉丝: 55

最新资源

- DedeAMPZ PHP整合环境安装包:一键配置简单快捷

- 图片格式转换器v6.1:强大功能与易用性并存

- VB.net2005实现GPIB32接口模块编程指南

- HTML领域内的咖啡先生Mr.Coffee解析

- 利用ID3算法实现决策树分类及可视化应用

- Delphi和BCB用户必备:ODAC_6.25控件安装教程

- C++开发的工资管理系统及其数据库应用

- 虚拟硬盘大师:创建及管理虚拟硬盘工具

- Visual SVN在线管理界面系统SVN ADMIN源码发布

- MapReduce实现PageRank算法原理与应用

- 12864液晶编码工具:自制文字图像处理程序

- JavaScript压缩包子技术的应用与探索

- UDP收发程序:网络编程初学者的最佳实践

- SQL Server 2005 卸载工具详细指南

- .NET 3.5图形控件使用与绘图技巧分享

- 构建ASP.NET+SQL2005的高效物流信息管理系统