参数 最小值 典型值 最大值 单位

1

测试条件/注释

V

DD

= 3 V(正常模式) 1.1 mA I/O0至I/O7为DAC,内部基准电压源,

增益 = 1

1 mA I/O0至I/O7为DAC,外部基准电压源,

增益 = 1

I/O0至I/O7为DAC并由ADC采样,

内部基准电压源,增益 = 1

0.78 mA I/O0至I/O7为DAC并由ADC采样,

外部基准电压源,增益 = 1

0.75 mA I/O0至I/O7为ADC,内部基准电压源,

增益 = 1

0.5 mA I/O0至I/O7为ADC,外部基准电压源,

增益 = 1

0.45 mA I/O0至I/O7为通用输出

0.45 mA I/O0至I/O7为通用输入

1

除非另有说明,所有用分贝(dB)表示的规格均参考满量程输入(FSR),并用低于满量程0.5 dB的输入信号进行测试。

2

通过设计和特性保证,但未经生产测试。

3

除非另有说明,直流规格均在输出端无负载的情况下测得。线性度计算使用8至4095的代码范围。当V

REF

= V

DD

时,存在一个10 mV的上行死区。

4

从任一供电轨吸取负载电流时,相对于该供电轨的输出电压裕量受输出器件的25 Ω典型通道电阻限制。例如,当吸电流为1 mA时,

最小输出电压 = 25 Ω × 1 mA = 25 mV(见图32)。

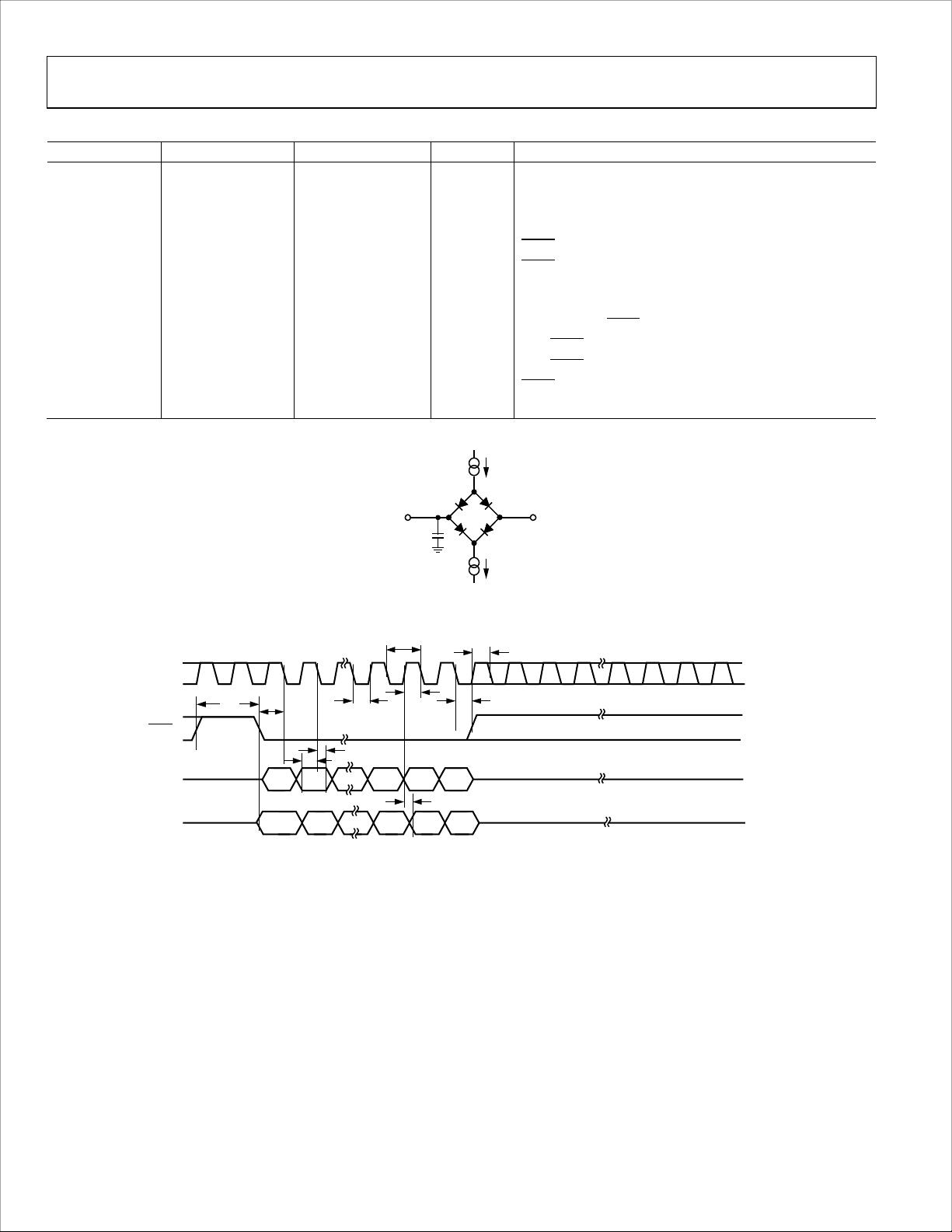

表3. AD5592R时序特性

参数 2.7 V ≤ V

DD

< 3 V 3 V ≤ V

DD

≤ 5.5 V 单位 测试条件/注释

t

1

33 20 ns(最小值) SCLK周期时间(写操作)

50 50 ns(最小值) SCLK周期时间(读操作)

t

2

16 10 ns(最小值) SCLK高电平时间

t

3

16 10 ns(最小值) SCLK低电平时间

t

4

15 10 ns(最小值)

SYNC到SCLK下降沿建立时间

2 2 µs(最大值)

SYNC到SCLK下降沿建立时间

t

5

7 7 ns(最小值) 数据建立时间

t

6

5 5 ns(最小值) 数据保持时间

t

7

15 10 ns(最小值) SCLK下降沿到SYNC上升沿

t

8

30 30 ns(最小值) 最小SYNC高电平时间(寄存器写操作)

60 60 ns(最小值) 最小SYNC高电平时间(寄存器读操作)

t

9

0 0 ns(最小值)

SYNC上升沿到下一个SCLK下降沿

t

10

25 25 ns(最大值) SCLK上升沿到SDO有效

Rev. A | Page 7 of 40

AD5592R

时序特性

通过设计和特性保证,未经生产测试。除非另有说明,所有输入信号均在t

R

= t

F

= 5 ns(10%至90%的V

DD

)情况下标定并从

(V

IL

+ V

IH

)/2电平起开始计时,T

A

= T

MIN

至 T

MAX

。