DDR硬件设计指南:Layout要点与DDR2详解

"DDRLayoutGuide, SDRAM, DDR, DDR2, DDR3, hardware design, layout guidelines, clock, data rate, Micron, Freescale, VSS, VSSQ, VDD, VDDDQ, signal groups, PCB stackups"

DDR(Double Data Rate)内存是现代计算机和嵌入式系统中广泛使用的高速存储技术。DDR、DDR2和DDR3代表了这一技术的三个主要发展阶段。SDRAM(Synchronous Dynamic Random-Access Memory)通常是较旧的设计,适用于对速度要求不那么高的应用。相比之下,DDR2逐渐取代DDR,而DDR3则进一步提升了速度和效率。

DDR内存的工作原理主要区别在于其内部的预取技术,这是影响其性能的关键因素。虽然内部机制有所不同,但从外部接口来看,这些内存类型的基本结构相似,包括时钟(clock)、数据(data)、地址(address)、控制(control)和命令(command)信号。DDR内存的数据速率通常基于时钟频率的一半计算,因为每个时钟周期传输两次数据(上升沿和下降沿),所以如果时钟频率是266MHz,那么数据速率也是266MHz,而不是533MHz的比特率。

DDR/DDR2/DDR3的布局指南是硬件工程师设计高速内存系统时的重要参考。这些指南通常包括如何处理电源、地线、信号路由以及印制电路板(PCB)的设计。例如,Micron和Freescale等公司提供了具体的Design Guidelines,强调了VSS(数字地)和VSSQ(信号地)、VDD(内核电源)和VDDDQ(DQ和I/O电源)的使用。在没有特殊说明的情况下,这些电源通常被视为等效。

在DDR内存的信号组织中,有以下几个关键信号组:

1. 数字信号组:DQ(数据)、DQS(数据 strobe)和DM(数据掩码),其中DQ和DQS通常按字节分组,例如DQ0~DQ7和DQS0,每个字节又包含一个通道Lane。

2. 地址信号组:ADDRESS,用于指定内存位置。

3. 命令信号组:包括CAS#(行地址选择)、RAS#(列地址选择)和WE#(写使能)。

4. 控制信号组:CS#(片选)和CKE(时钟使能)。

5. 时钟信号组:CK(时钟)和CK#(时钟反相)。

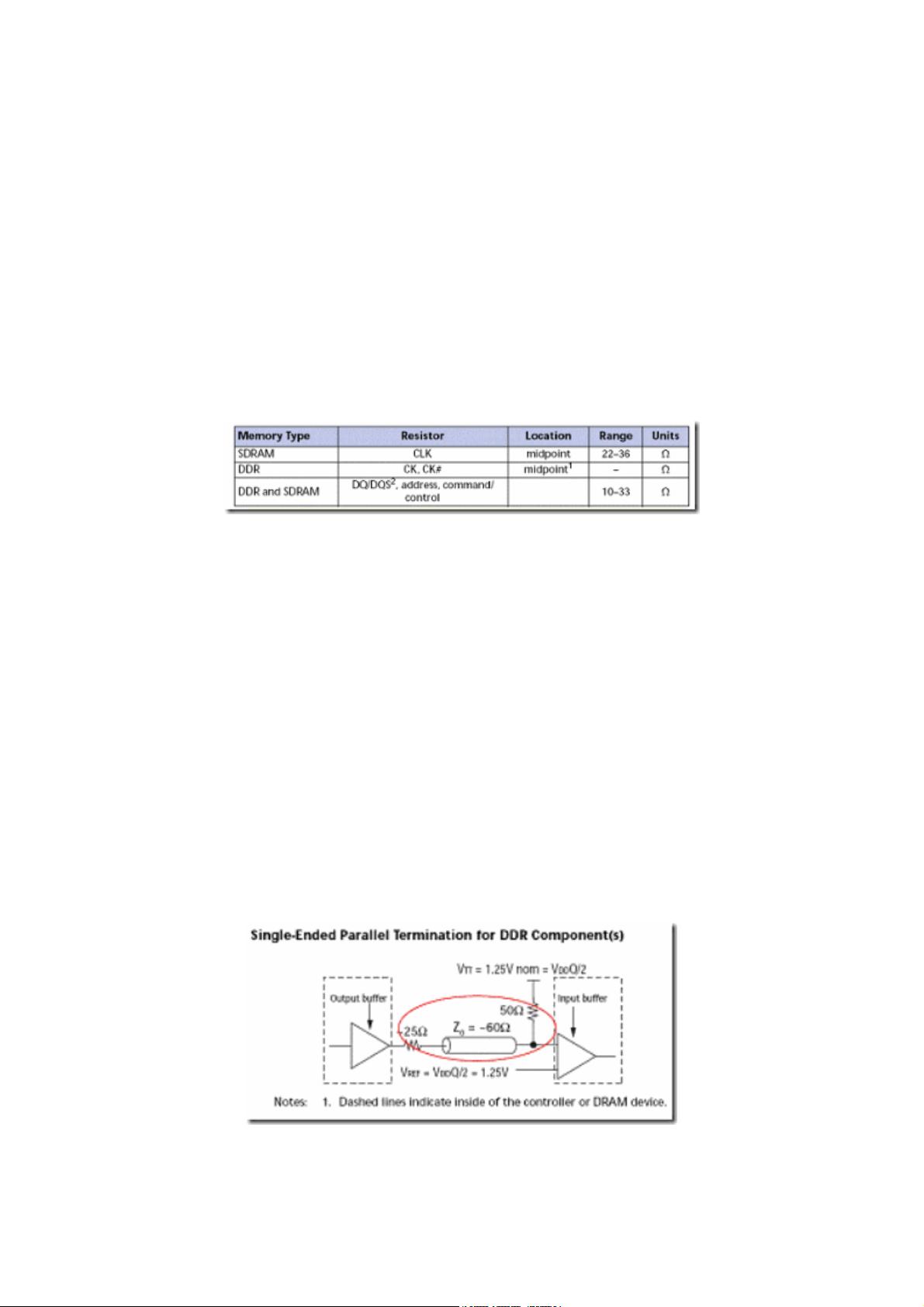

在PCB设计方面,推荐使用6层电路板,其中阻抗控制在50至60欧姆,以确保信号的完整性。电路板的厚度也会影响信号传输的质量,通常选择1.5英寸的厚度。这样的设计有助于减少信号干扰,提高系统的稳定性和性能。

DDR的硬件设计涉及到多个层面,包括内存类型的特性理解、信号路由的最佳实践、电源管理以及PCB的物理布局。对于硬件工程师,特别是初学者,理解和遵循这些规则是至关重要的,它们能够确保设计出高效、可靠的高速内存系统。

相关推荐

jie3080

- 粉丝: 0

最新资源

- 桌面玫瑰恶搞小程序,带给你不一样的开心惊喜

- Win7系统语言栏无法显示?一键修复解决方案

- 防止粘贴非支持HTML的Quill.js插件

- 深入解析:微软Visual C#基础教程

- 初学者必备:超级玛丽增强版源码解析

- Web天气预报JavaScript插件使用指南

- MATLAB图像处理:蚁群算法优化抗图像收缩技术

- Flash AS3.0打造趣味打地鼠游戏

- Claxed: 简化样式的React样式组件类

- Docker与Laravel整合:跨媒体泊坞窗的设置与配置

- 快速搭建SSM框架:Maven模板工程指南

- 网众nxd远程连接工具:高效便捷的远程操作解决方案

- MySQL高效使用技巧全解析

- PIC单片机序列号编程烧录工具:自动校验与.num文件生成

- Next.js实现React博客教程:日语示例项目解析

- 医院官网构建与信息管理解决方案