TDC-GPX

acam-messelectronic gmbh - Am Hasenbiel 27 - D-76297 Stutensee-Blankenloch - Germany - www.acam.de

10

1.3.5 General Timings & Resolution

The TDC-GPX time measurement is based on internal

propagation delays. Those delays depend on tempera-

ture and voltage. They also vary over the production

lots. The resolution adjust mode (see) uses the voltage

dependency to compensate for temperature and pro-

duction variations and sets the circuits to a fixed and

programmable resolution.

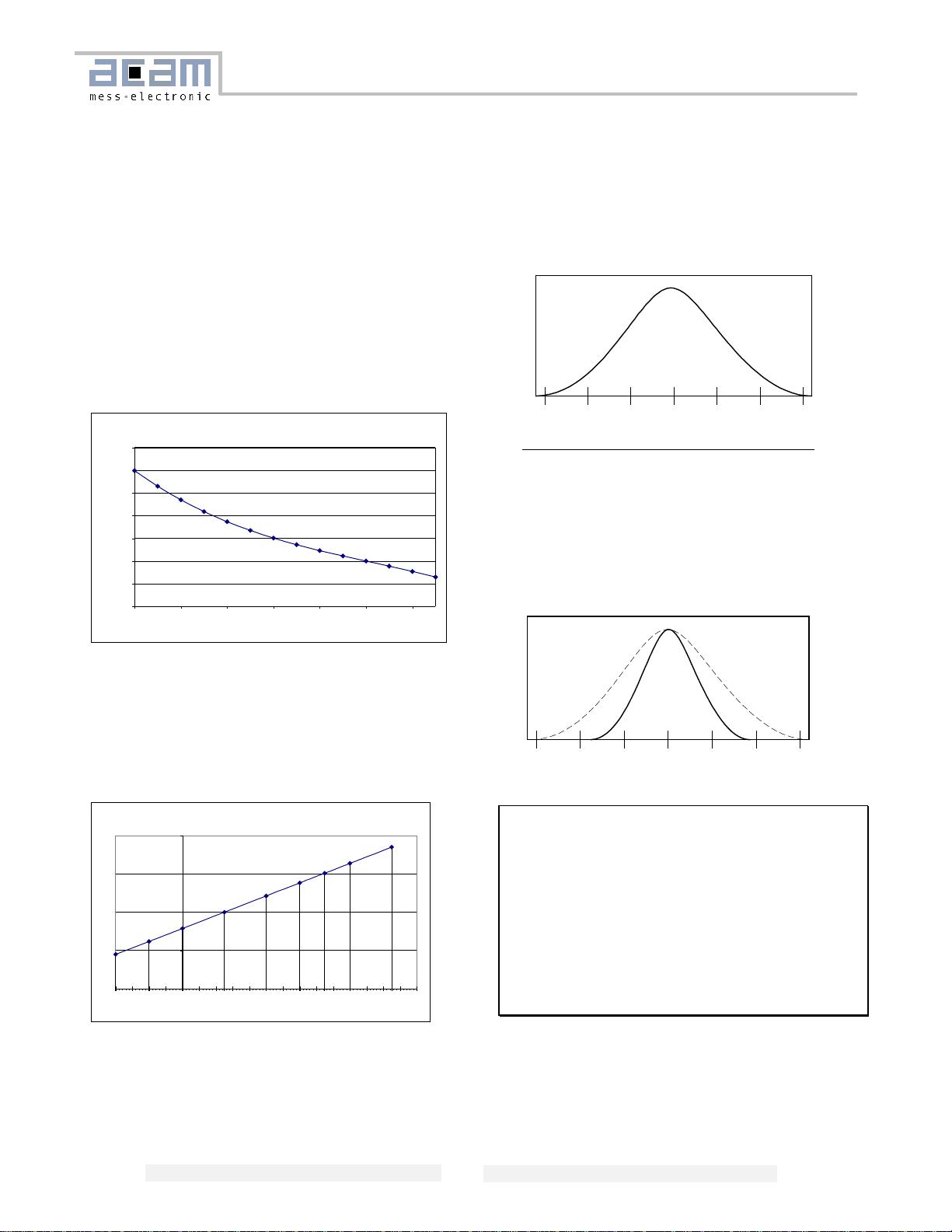

Figure 9 shows the dependency of all timings from the

core voltage, referred to the 3.3V timings. The resolu-

tion at 3.3V can be varied by factors 0.93 at 3.6V to

1.4 at 2.3V.

Delay Variation Dependency on Power Supply Voltage

1,40

1,33

1,27

1,22

1,17

1,13

1,10

1,07

1,05

1,02

1,00

0,98

0,95

0,93

0,80

0,90

1,00

1,10

1,20

1,30

1,40

1,50

2,3 2,5 2,7 2,9 3,1 3,3 3,5

Vddc

δ

δ

δ

δt

Figure 9

Figure 10 shows the dependency of all timings on the

temperature, referred to 25°C junction temperature. If

the temperature increases from 25°C to 70°C, the

intrinsic resolution goes down by a factor 1.077. In

resolution adjust mode this is compensated by increas-

ing the core voltage from 3.3V to 3.6V.

Delay Variation Dependency on Temperature

0,889

0,923

0,957

1,000

1,043

1,077

1,102

1,128

1,170

0,800

0,900

1,000

1,100

1,200

-40 -30 -20 -10 0 10 20 30 40 50 60 70 80 90 100 110 120 130 140

Tj(°C)

dt

Figure 10

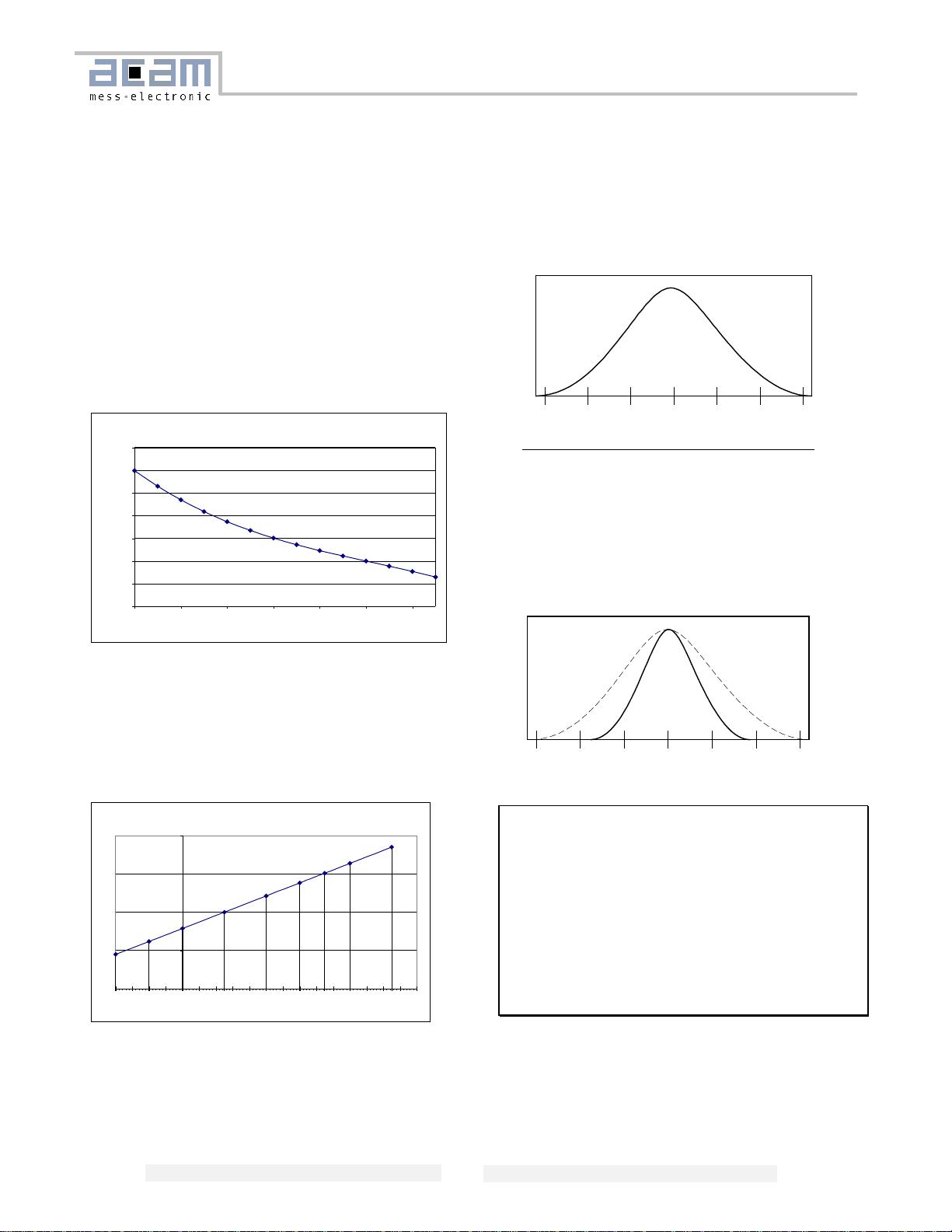

Without resolution adjust, the intrinsic resolution var-

ies slightly from chip to chip. The distribution over the

production lots is of gaussian type.

-3σ

-2σ -1σ 01σ 2σ

3σ

Typical

(1.0)

Worst

(1.31)

Best

(0.74)

81ps

60ps 104ps

# of chips

(@Vddc = 3.3V, Tamb = 25°C)

Figure 11

Within a single production lot the distribution is nar-

rower. Figure 12 shows a typical distribution of the

intrinsic resolution at 3.3 V core voltage and 25°C

ambient temperature within a single production lot.

81ps

70ps 92ps

# of chips

(@Vddc = 3.3V, Tamb = 25°C)

Figure 12

Example:

Taking the distribution from Figure 12 and assuming

an operating temperature range of 0°C to 40°C as

well as 1 Mhz data rate. The junction temperature will

be about 57°C max. The slowest chips will have 92ps

* 1.043 = 97ps resolution at 3.3V Vddc. Increasing

the core voltage to 3.6V will speed them up to 90.2ps.

Setting the resolution adjust mode to a resolution of

95ps will guarantee that the PLLs of all chips will lock

at one and the same resolution over the whole operat-

ing temperature range.