曼彻斯特编码Verilog FPGA实现与优点探讨

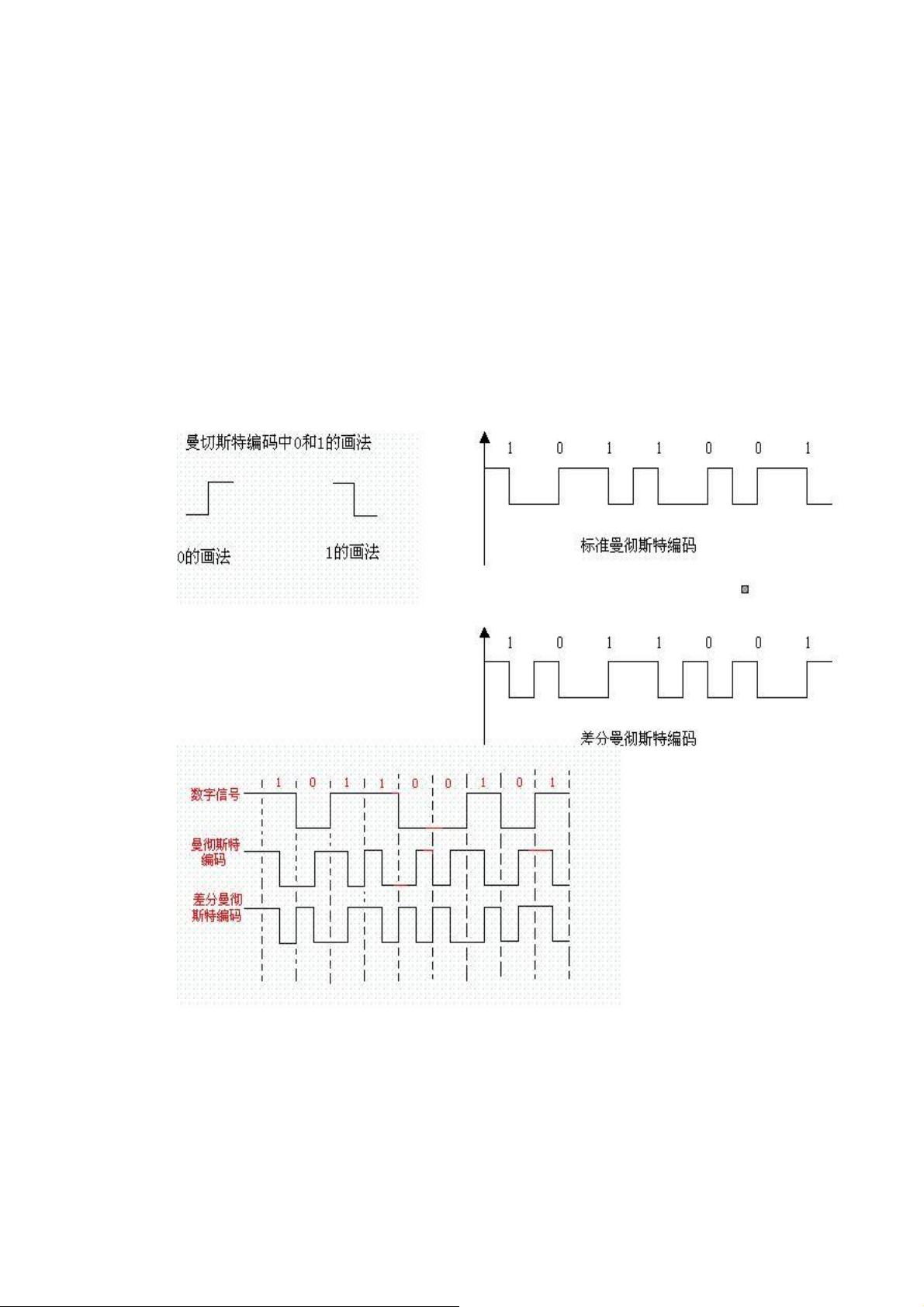

曼彻斯特编解码是一种在数据传输中同时包含时钟信息的编码方式,它通过在每个码元中插入一个跳变,实现了自同步和抗干扰性能。曼彻斯特编码的特点是每个码元由两个电平组成,导致数据传输速率仅为调制速率的一半,但考虑到LVDS端口的高速传输特性,这种牺牲是可以接受的。编码格式中,上跳变对应0,下跳变对应1,以特定模式111000开头,没有跳变的11或00用于表示结束或中断。

在实际应用中,传统的实现方式如使用单片机的串行I/O口或专用曼彻斯特编码译码器(如HD15530)存在局限性。例如,它们仅能进行奇偶校验,难以处理突发性错误;速率和帧有效数据位数有限;在高速传输场景下,难以满足需求。随着VHDL和现场可编程逻辑器件(FPGA)的普及,数字系统设计变得更加灵活,这为曼彻斯特编解码提供了新的解决方案。

曼彻斯特编码器的设计思路中,采用了双倍于数据位宽的同步时钟,以确保编码的准确性。编码过程包括:首先检查接口FIFO是否为空,若非空则输出同步头111000,接着读取FIFO数据并计数,当达到预设长度时停止读取并开始新的同步头。如果未达到预定长度,将用0填充以完成当前帧。此外,设计还包括状态机来控制数据的输出,如Valid信号用于标记数据是否有效,以及根据RD_COUNT变量调整编码输出,如1变为10,0变为01。

曼彻斯特编码的实现不仅涉及硬件电路的设计,还包含了软件逻辑的协同工作,如通过状态机管理数据流和同步信息的插入。该设计的关键在于利用FPGA的并行处理能力,提高了编码的效率和灵活性,使得曼彻斯特编码能在现代高速电子系统中得到广泛应用,尤其是在以太网和短距离无线通信等需要稳定同步的场景中。通过这种方式,数据传输的准确性和可靠性得到了显著提升。

2018-05-10 上传

2023-04-21 上传

2022-05-27 上传

2019-08-27 上传

2021-01-13 上传

2021-11-24 上传

点击了解资源详情

LK

- 粉丝: 23

- 资源: 5

最新资源

- iReport實作(ireportteach.pdf)

- javascript万能table合并单元格,隐藏列 html版

- 软件 46家公司的笔试题目

- Keil C51微处理器开发工具使用指南

- jasperreport与ireport的配置与使用

- 历年一级 机试 试题.doc

- 51 单片机C 语言入门教程 pdf

- 更改2003上传限制

- 戏说面向对象程序设计C#版

- Microsoft.NET Remoting权威指南

- Dreamweaver网页设计制作论文

- ECMA 2.62手册

- 无线传感网中能耗因素的分析与仿真

- MS+SQL+Server中大数据量表的查询优化

- eclipse快捷键大全

- WiMAXWave2的双信道MIMO测量 .doc