DS176 October 16, 2012 www.xilinx.com 1

Advance Product Specification

© Copyright 2011–2012 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are

trademarks of Xilinx in the United States and other countries. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are trademarks of

ARM in the EU and other countries. All other trademarks are the property of their respective owners.

Introduction

The Xilinx

®

7 series FPGAs memory interface solutions

cores provide high-performance connections to DDR3

and DDR2 SDRAMs, QDRII+ SRAM, and

RLDRAM II/RLDRAM III.

DDR3 and DDR2 SDRAMs

This section discusses the features, applications, and

functional description of Xilinx 7 series FPGAs memory

interface solutions in DDR3 and DDR2 SDRAMs. These

solutions are available with an optional AXI4 slave

interface.

DDR3 SDRAM Features

• Component support for interface widths up to 72 bits

• Single and dual rank UDIMM, RDIMM, and

SODIMM support

• DDR3 (1.5V) and DDR3L (1.35V)

• 1, 2, and 4 Gb density device support

• 8-bank support

• x8 and x16 device support

• 8:1 DQ:DQS ratio support

• Configurable data bus widths (multiples of 8, up to

72 bits)

• 8-word burst support

• Support for 5 to 14 cycles of column-address strobe

(CAS) latency (CL)

• On-die termination (ODT) support

• Support for 5 to 10 cycles of CAS write latency

• ZQ calibration – initial and periodic (configurable)

• Write leveling support for DDR3 (fly-by routing

topology required for DDR3 component designs)

• JEDEC-compliant DDR3 initialization support

• Source code delivery in Verilog and VHDL (top-level

files only)

• 4:1 and 2:1 memory to FPGA logic interface clock

ratio

• ECC support

• I/O Power Reduction option reduces average I/O

power by automatically disabling DQ/DQS IBUFs

and internal terminations during writes and periods

of inactivity

• Internal V

REF

support

• Multicontroller support for up to eight controllers

• Two controller request processing modes:

• Normal: reorder requests to optimize system

throughput and latency

• Strict: memory requests are processed in the

order received

7 Series FPGAs

Memory Interface Solutions (v1.7)

DS176 October 16, 2012 Advance Product Specification

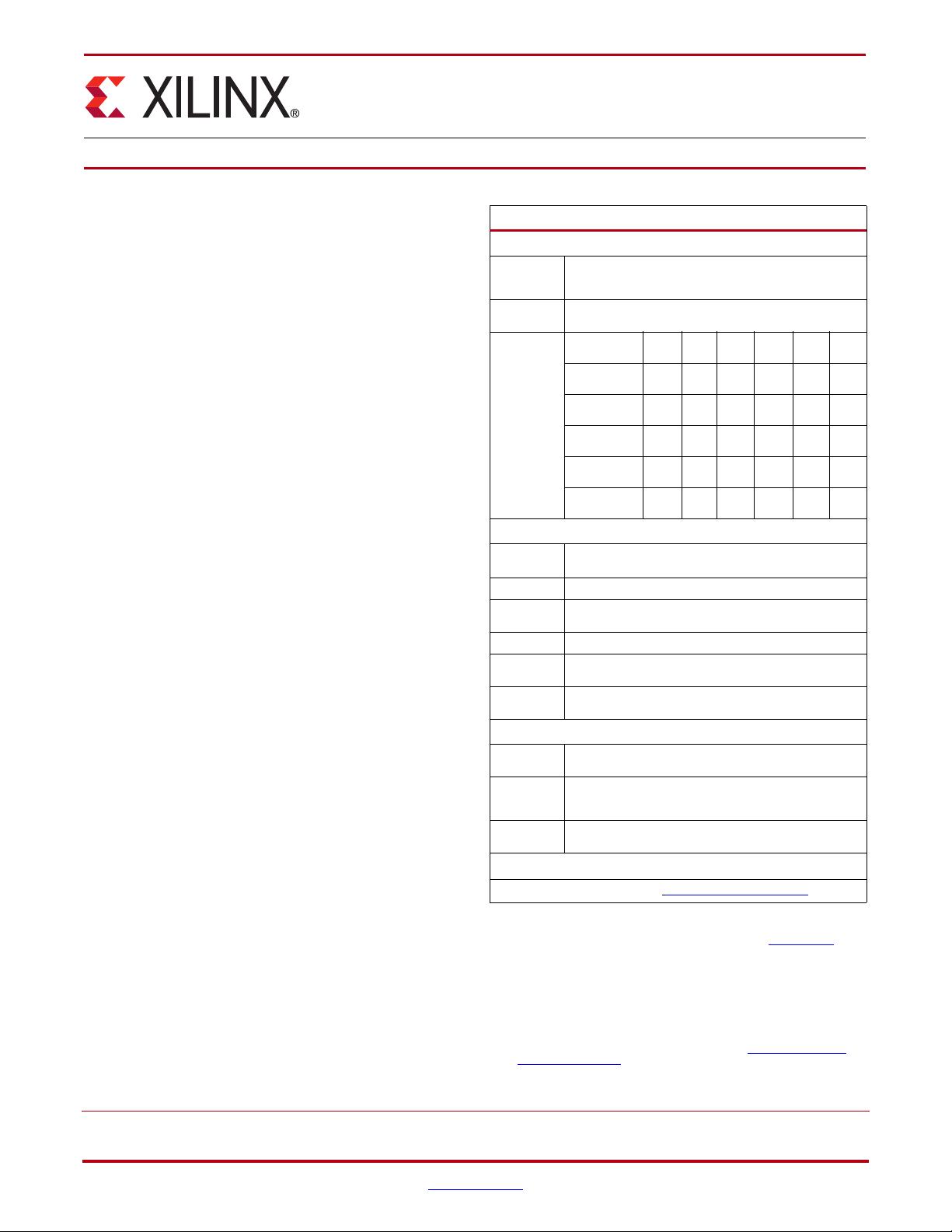

LogiCORE™ IP Facts Table

Core Specifics

Supported

Device

Family

(1)

Zynq™-7000

(2)

, Artix™-7, Virtex

®

-7

(3)

, and Kintex™-7

(3)

Supported

Memory

DDR3 Component and DIMM, DDR2 Component and DIMM,

QDRII+, and RLDRAM II Components

Resources

Product

(4)

LUTs

Flip-

Flops

BUFG

PLLE2

MMCM

Block

RAM

7 Series FPGAs

DDR3 SDRAM

10,554 6,682 2 1 1 0

7 Series FPGAs

DDR2 SDRAM

7,633 4,588 2 1 1 0

7 Series FPGAs

QDRII+ SRAM

2,536 2,117 2 1 1 0

7 Series FPGAs

RLDRAM II

5,134 3,308 2 1 1 0

7 Series FPGAs

RLDRAM III

8,731 5,259 2 1 1 0

Provided with Core

Documentation

Product Specification

User Guide

Design Files Verilog, VHDL (top-level files only)

Example

Design

Verilog, VHDL (top-level files only)

Test Bench Not Provided

Constraints

File

ISE: UCF

Vivado: XDC

Supported

S/W Driver

N/A

Tested Design Flows

(5)

Design Entry

ISE Design Suite v14.3

Vivado Design Suite v2012.3

(6)

Simulation

(Behavioral

only)

ISim

(7)

(Verilog designs only), Mentor Graphics ModelSim

Vivado Simulator

(7)

Synthesis XST, Synopsys Synplify Pro

Vivado™ Synthesis

Support

Provided by Xilinx @ www.xilinx.com/support

Notes:

1. For a complete listing of supported devices, see the release notes for

MIG.

2. Supported in ISE® Design Suite implementations only.

3. See the Virtex-7 FPGAs Data Sheet: DC and Switching Characteristics or

the Kintex-7 FPGAs Data Sheet: DC and Switching Characteristics for

performance information.

4. Resource utilization can change depending on the options chosen,

memory device used, or both. Resource information is provided for 72-bit

DDR3 SDRAM, 72-bit DDR2 SDRAM, 36-bit QDRII+ SRAM, 72-bit

RLDRAM II, and 72-bit RLDRAM III interfaces.

5. For the supported versions of the tools, see the Xilinx Design Tools:

Release Notes Guide.

6. Supports only 7 series devices.

7. ISim and Vivado Simulators are supported for DDR3 SDRAM, DDR2

SDRAM, QDRII+ SRAM, and RLDRAM II.