提升FPGA时序设计:完美时序指南

需积分: 32 23 浏览量

更新于2024-07-28

收藏 4.13MB PDF 举报

"《完美时序(中)》是一本专注于时钟产生和分发设计的专业指南,旨在帮助FPGA开发人员提升设计水平。作者站在工程师的角度出发,强调在高速数字设计中,时钟电路的优化至关重要,尤其是在追求高速度的同步系统设计中。书中深入探讨了时钟发生器、时钟分发网络的核心组件,如低偏斜输出和零延时缓冲器,这些器件对于提供纯净、稳定的时钟信号,确保系统中各部分设备同步运行具有决定性作用。

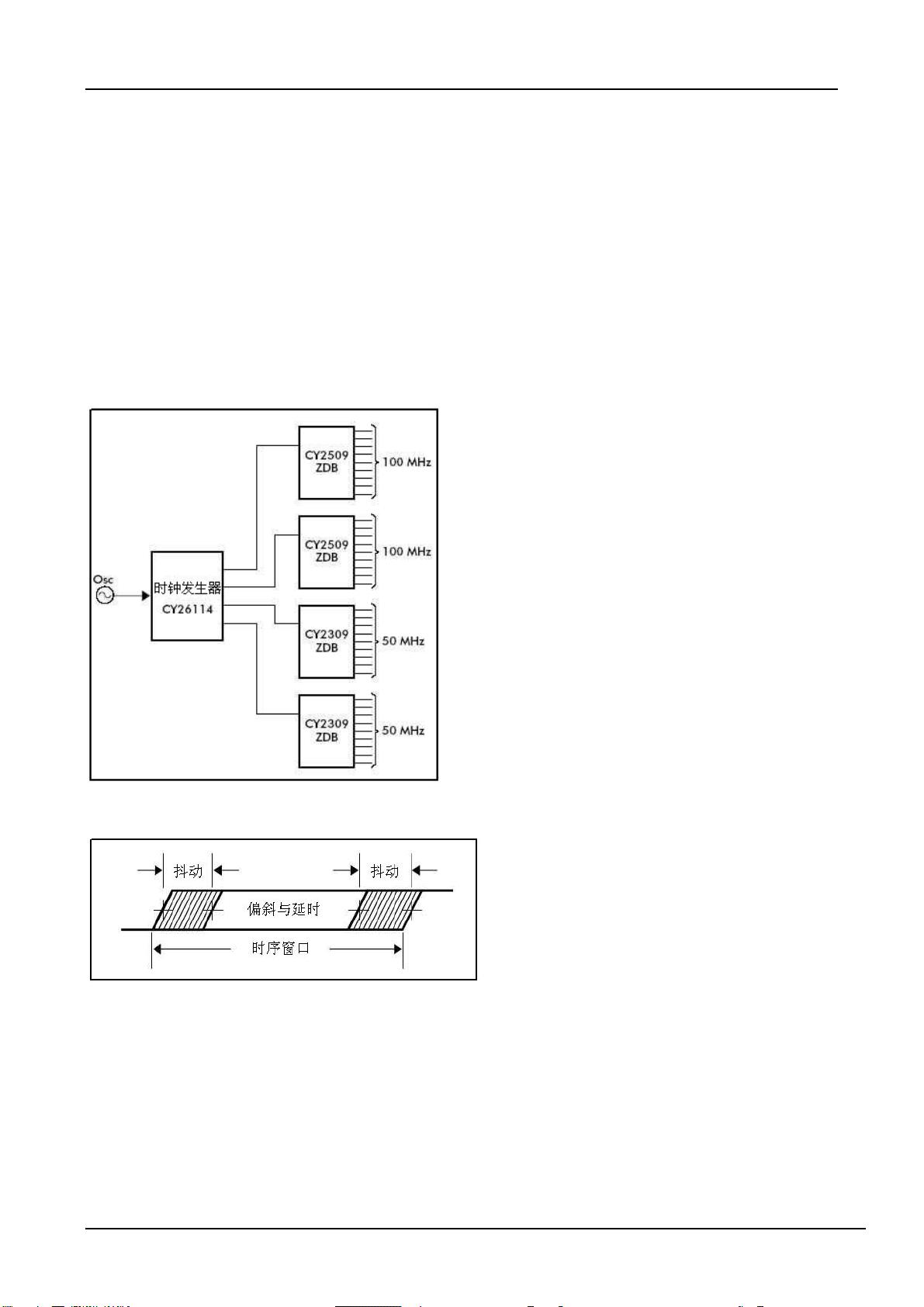

章节一介绍了时钟设计的基本理念,包括如何选择最适合的方法和技术,以及如何应对不断增长的时钟需求,如多种频率的同步和多副本产生。设计者需要关注时钟间的相位一致性,以避免周期时间的浪费,这时专用的时钟缓冲器和锁相环就显得尤为重要。它们不仅提供精确的时钟信号,还能通过调整时钟边缘对齐和时间延迟补偿,增强设计的灵活性。

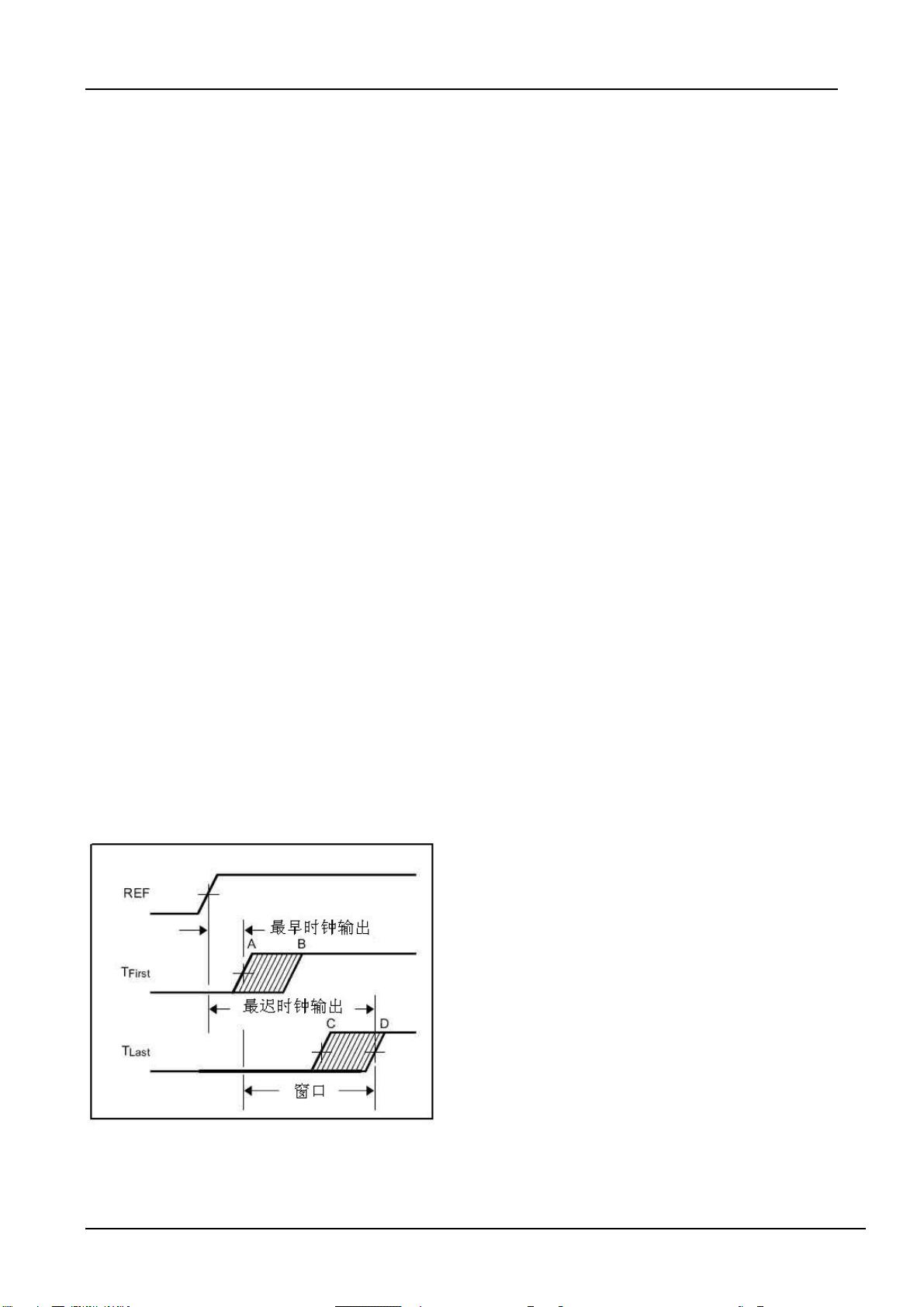

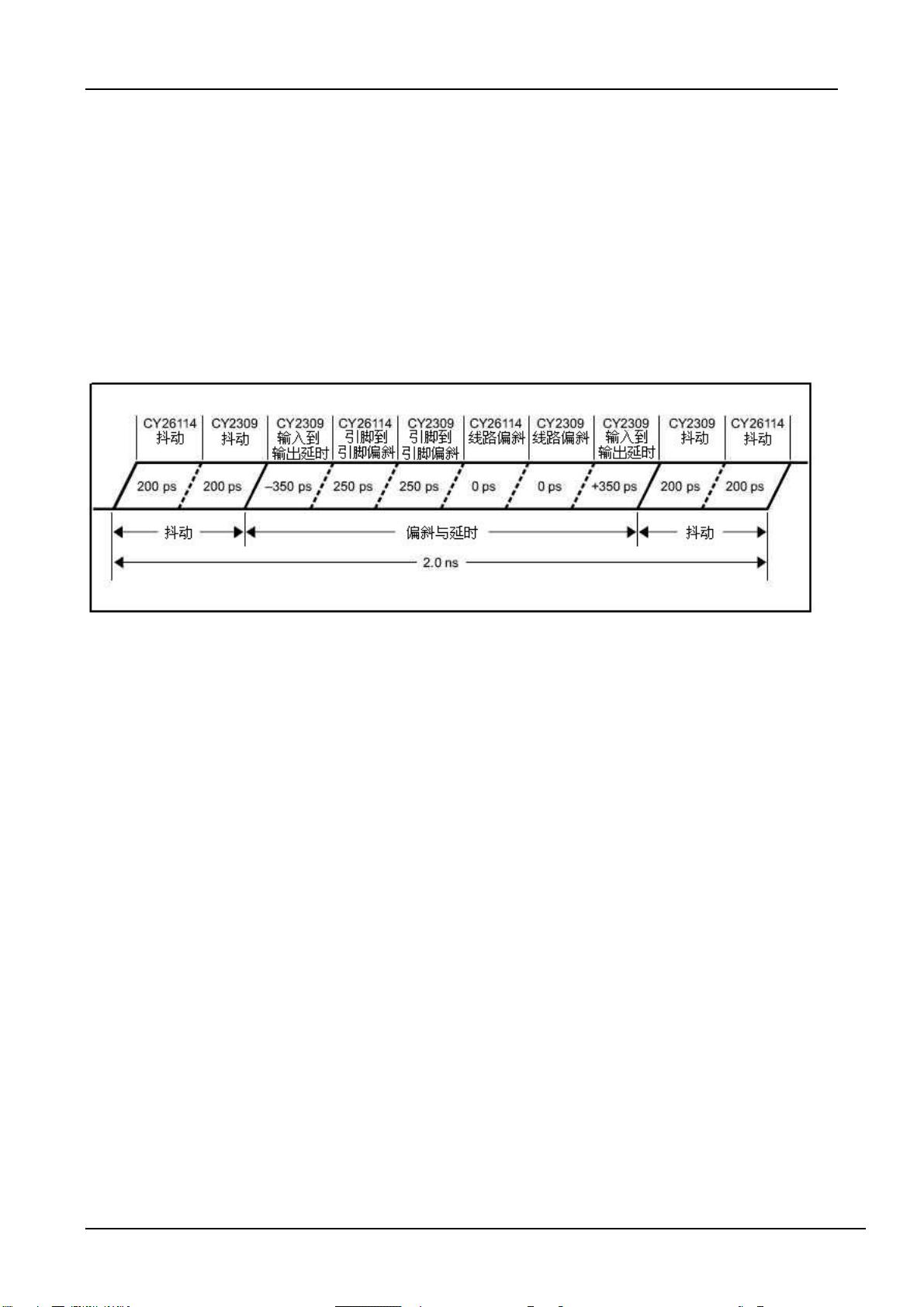

第二章详细解析了低偏斜输出和零延时缓冲器,这两种基础元件在创建对称且纯净的时钟信号方面扮演着关键角色,它们是实现时序准确性的基石。同步系统中的时序预算是一个关键概念,第三章深入讨论了计算时序裕度时要考虑的各种因素,包括抖动、偏斜、相位误差等动态变量。通过理解这些变量之间的相互影响,设计者可以利用总时序预算这一工具来平衡周期时间,避免过度预留导致性能浪费。

第四章专门聚焦于抖动这个常见但容易误解的概念,解释其定义和测量方法,帮助设计师澄清关于抖动的误区。书中详尽探讨了不同类型抖动的来源和特性,为准确评估和控制时钟质量提供了实用的指导。

《完美时序(中)》是一本综合性的教程,旨在提供实用的策略和方法,帮助FPGA开发人员在面对高速时钟设计挑战时,能够优化时序,提升电路性能,确保系统的稳定性和可靠性。"

2009-04-29 上传

2011-12-20 上传

2007-07-30 上传

2019-07-26 上传

2015-06-09 上传

2009-03-04 上传

2011-02-19 上传

2009-02-12 上传

2009-08-28 上传