PLL技术解析:相位噪声与无线设计考量

需积分: 48 59 浏览量

更新于2024-07-14

收藏 6.3MB PDF 举报

"PLLs, Clocking, and Clock Distribution - ISSCC 2021 Short Course由UCLA的Behzad Razavi教授讲解,主要涵盖PLL的基础、不完美性、相位噪声、建模以及无线设计的关键考虑因素。课程大纲包括PLL的基本原理、PLL的不完善性、相位噪声在PLL中的角色、PLL模型建立以及无线设计的考量。不过,课程不会涉及数字PLL、亚采样PLL、基本构建块的设计和射频综合等内容。"

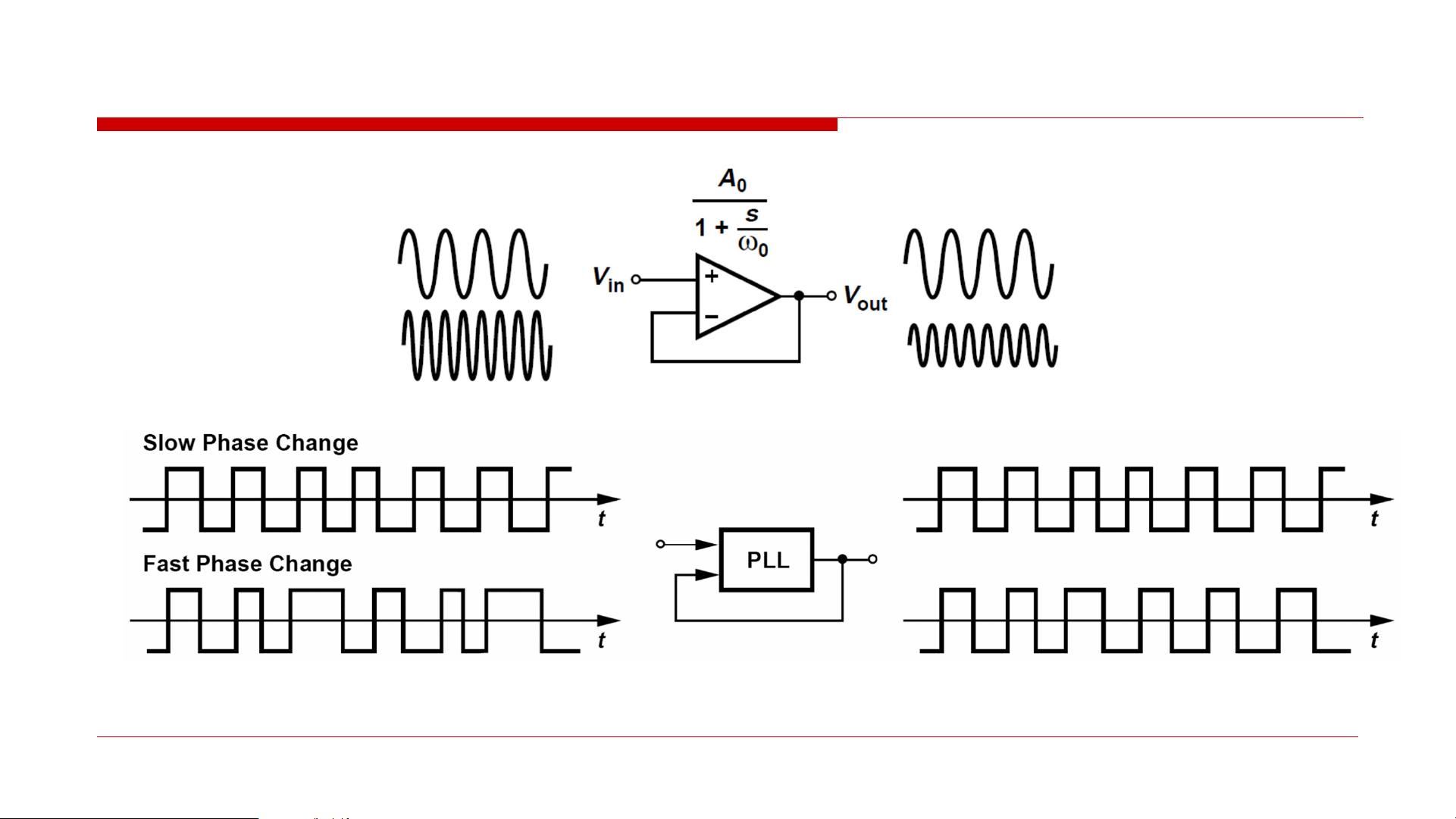

PLL(锁相环)是模拟和数字通信系统中的核心组件,用于频率合成和时钟恢复。在"PLL Fundamentals"部分,Razavi教授可能会讨论PLL的基本结构,它通常包括鉴相器(Phase Detector)、低通滤波器(Low-Pass Filter)和电压控制振荡器(Voltage-Controlled Oscillator,VCO)。鉴相器比较参考信号和VCO产生的信号之间的相位差,低通滤波器平滑误差电压并提供给VCO,以调整其输出频率,使两信号保持同步。

"PLL Imperfections"部分将深入探讨实际PLL系统中可能出现的问题,如非线性响应、锁定时间、相位裕度和频率裕度等。这些不完美可能会影响PLL的性能,包括相位噪声和频率稳定性的降低。

"Phase Noise in PLLs"是一个关键主题,因为相位噪声是衡量信号纯净度的重要指标,特别是在高频率和无线通信应用中。PLL的相位噪声来自多个来源,包括VCO、鉴相器和噪声引入的电路。理解相位噪声对于优化PLL设计至关重要。

"PLL Modeling"则可能涵盖如何建立数学模型来描述PLL的行为,以便进行仿真和分析。这通常涉及传递函数和状态空间模型,通过这些模型可以预测PLL在不同条件下的表现。

最后,"Wireless Design Considerations"将重点关注无线通信系统中PLL的应用,比如射频(RF)和基带信号处理的挑战。这可能包括相位噪声对调制质量的影响、功耗优化以及在多标准通信环境下的兼容性问题。

这个课程为学生和工程师提供了一个深入了解PLL工作原理、优化设计和解决实际问题的平台,对于那些致力于提高无线通信系统性能的专业人士来说,是一个宝贵的学习资源。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-03-23 上传

2021-03-23 上传

2021-03-23 上传

2024-03-16 上传

2021-03-23 上传

2021-03-23 上传

dogrush

- 粉丝: 16

- 资源: 32

最新资源

- 掌握JSON:开源项目解读与使用

- Ruby嵌入V8:在Ruby中直接运行JavaScript代码

- ThinkErcise: 20项大脑训练练习增强记忆与专注力

- 深入解析COVID-19疫情对HTML领域的影响

- 实时体育更新管理应用程序:livegame

- APPRADIO PRO:跨平台内容创作的CRX插件

- Spring Boot数据库集成与用户代理分析工具

- DNIF简易安装程序快速入门指南

- ActiveMQ AMQP客户端库版本1.8.1功能与测试

- 基于UVM 1.1的I2C Wishbone主设备实现指南

- Node.js + Express + MySQL项目教程:测试数据库连接

- tumbasUpk在线商店应用的UPK技术与汉港打码机结合

- 掌握可控金字塔分解与STSIM图像指标技术

- 浏览器插件:QR码与短链接即时转换工具

- Vercel部署GraphQL服务的实践指南

- 使用jsInclude动态加载JavaScript文件的方法与实践