Verilog实现编码器、计数器、译码器与多路选择器

下载需积分: 25 | DOCX格式 | 683KB |

更新于2024-07-18

| 125 浏览量 | 举报

"这篇内容主要介绍了如何使用Verilog语言来编写常见的数字逻辑组件,包括寄存器、计数器和3-8译码器。这些组件是数字系统设计的基础,对于理解和实现数字逻辑电路至关重要。"

在Verilog中,我们可以用模块(module)来定义这些组件。下面是对每个部分的详细解释:

1、寄存器(Register):

寄存器是一种存储数据的元件,通常用于暂时保存数据。在给定的代码中,`jicunqi`模块定义了一个8位寄存器,它有清零输入(clr)、时钟输入(clk)和数据输入(D)。寄存器的输出(DOUT)在每个时钟上升沿更新。如果清零信号为高,则DOUT被清零;否则,DOUT的值将等于数据输入D。测试代码模拟了不同的输入条件,以验证寄存器功能。

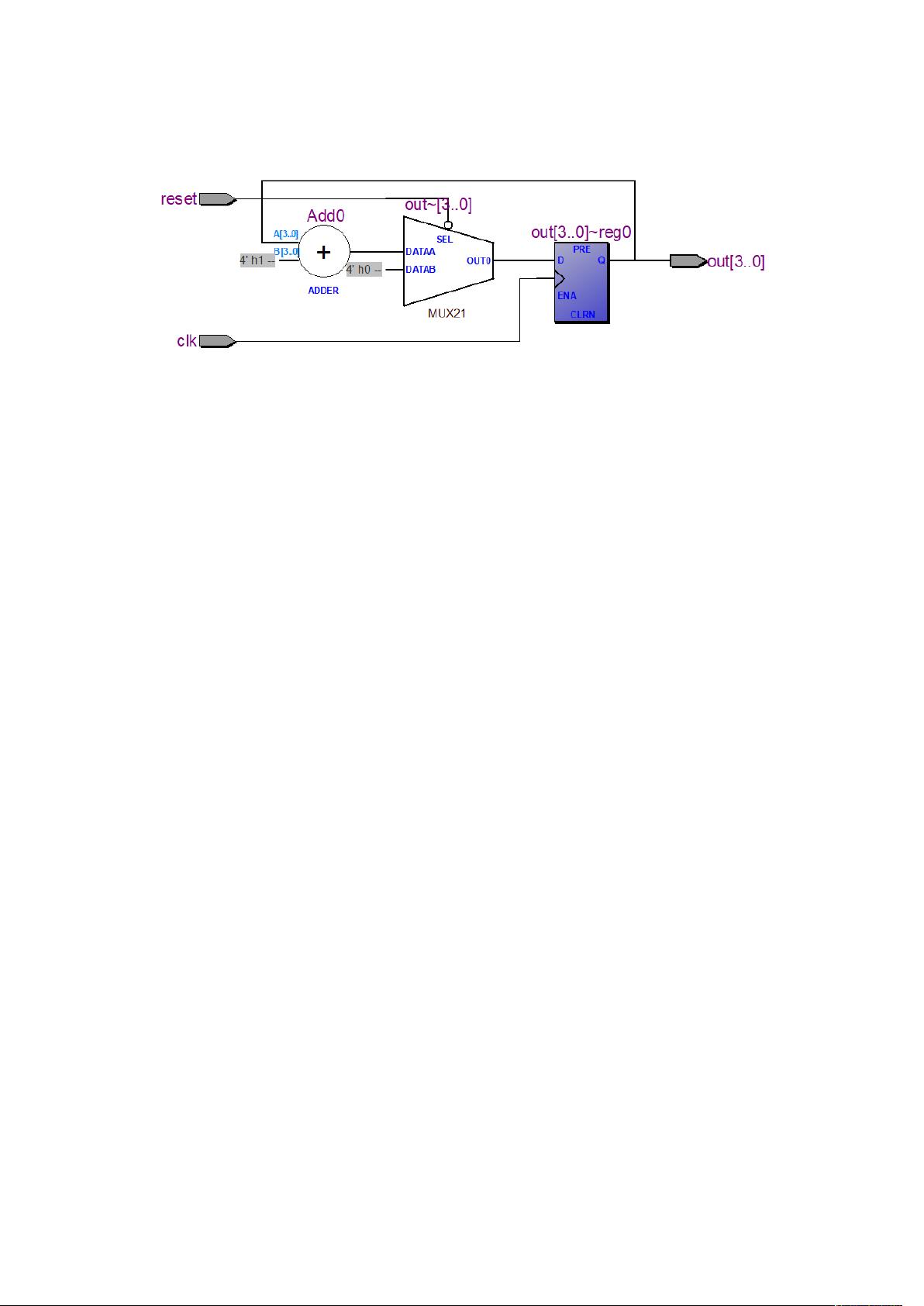

2、计数器(Counter):

计数器是能够递增或递减其输出的逻辑电路。这里展示的是一个4位的向上计数器`jishuqi`,它有复位(reset)、时钟(clk)和输出(out)。在每个时钟上升沿,如果没有复位信号,计数器的输出会增加1。测试代码首先设置时钟和复位信号,然后改变复位状态以测试计数器在不同状态下的行为。

3、3-8译码器(3-to-8 Decoder):

3-8译码器是一种多路选择器,它接收3位二进制输入(A),并根据输入值选择其8个输出(Y)中的一个变为高电平。在示例代码中,`yimaqi`模块通过case语句实现了这个功能。当输入A的不同组合时,对应的输出Y会激活。完整的3-8译码器的输出状态表通常会列出所有32种输入组合及其对应的8个输出状态。

以上组件都是数字逻辑设计的基础元素,它们可以组合成更复杂的系统,如处理器、内存和接口逻辑。了解如何用Verilog编写这些基本组件对于硬件描述语言的学习以及FPGA和ASIC设计是至关重要的。在实际应用中,这些组件通常会通过综合工具转换为实际的门级电路,以便在硬件上实现。

相关推荐

woshizhouzhouzhou

- 粉丝: 0

最新资源

- 革新操作体验:无需最小化按钮的窗口快速最小化工具

- VFP9编程实现EXCEL操作辅助软件的使用指南

- Apache CXF 2.2.9版本特性及资源下载指南

- Android黄金矿工游戏核心逻辑揭秘

- SQLyog企业版激活方法及文件结构解析

- PHP Flash投票系统源码及学习项目资源v1.2

- lhgDialog-4.2.0:轻量级且美观的弹窗组件,多皮肤支持

- ReactiveMaps:React组件库实现地图实时更新功能

- U盘硬件设计全方位学习资料

- Codice:一站式在线笔记与任务管理解决方案

- MyBatis自动生成POJO和Mapper工具类的介绍与应用

- 学生选课系统设计模版与概要设计指南

- radiusmanager 3.9.0 中文包发布

- 7LOG v1.0 正式版:多元技术项目源码包

- Newtonsoft.Json.dll 6.0版本:序列化与反序列化新突破

- Android实现SQLite数据库高效分页加载技巧