"FPGA系统设计中的Verilog数字UART串行控制器设计"

版权申诉

131 浏览量

更新于2024-02-29

收藏 1.67MB DOCX 举报

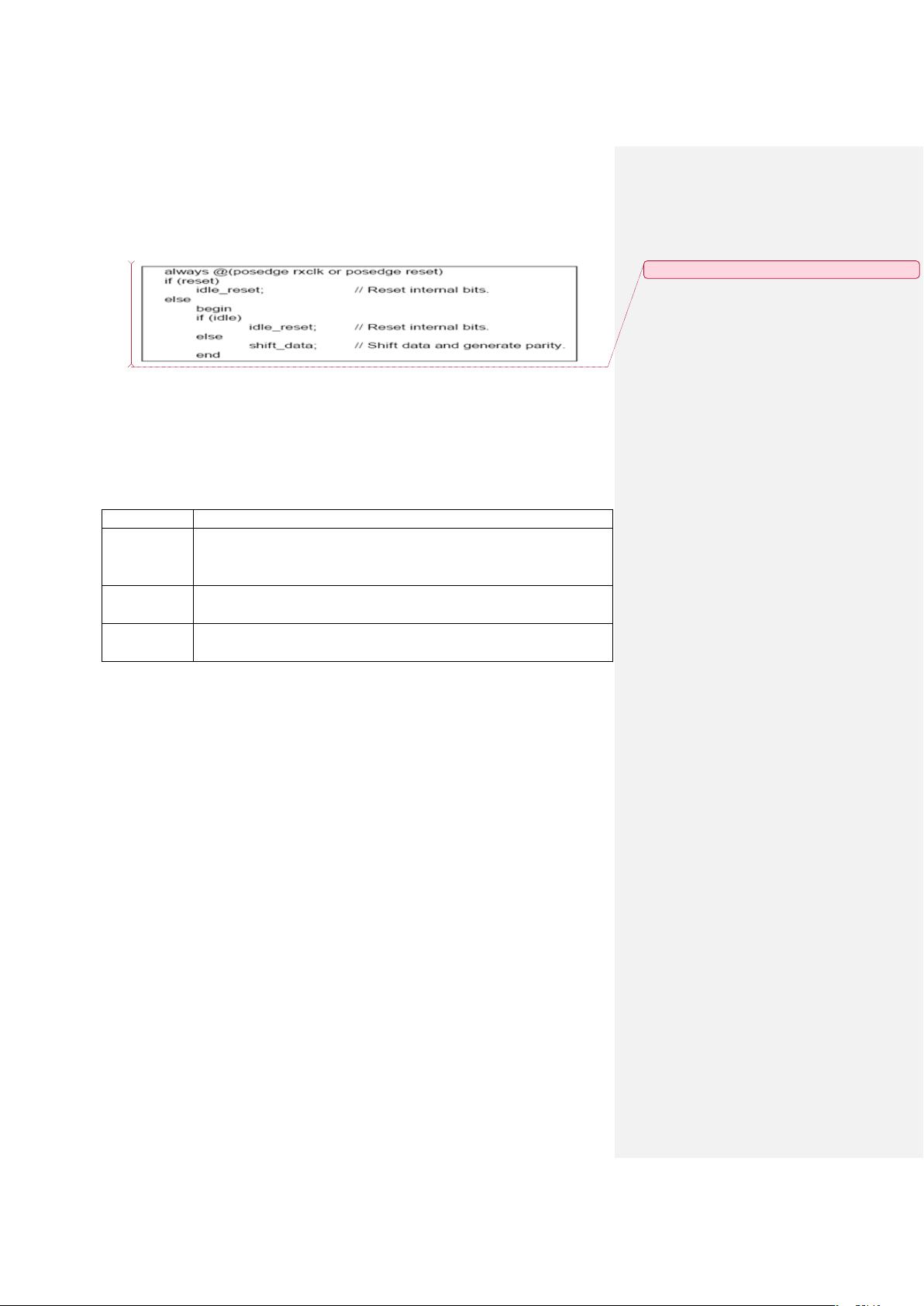

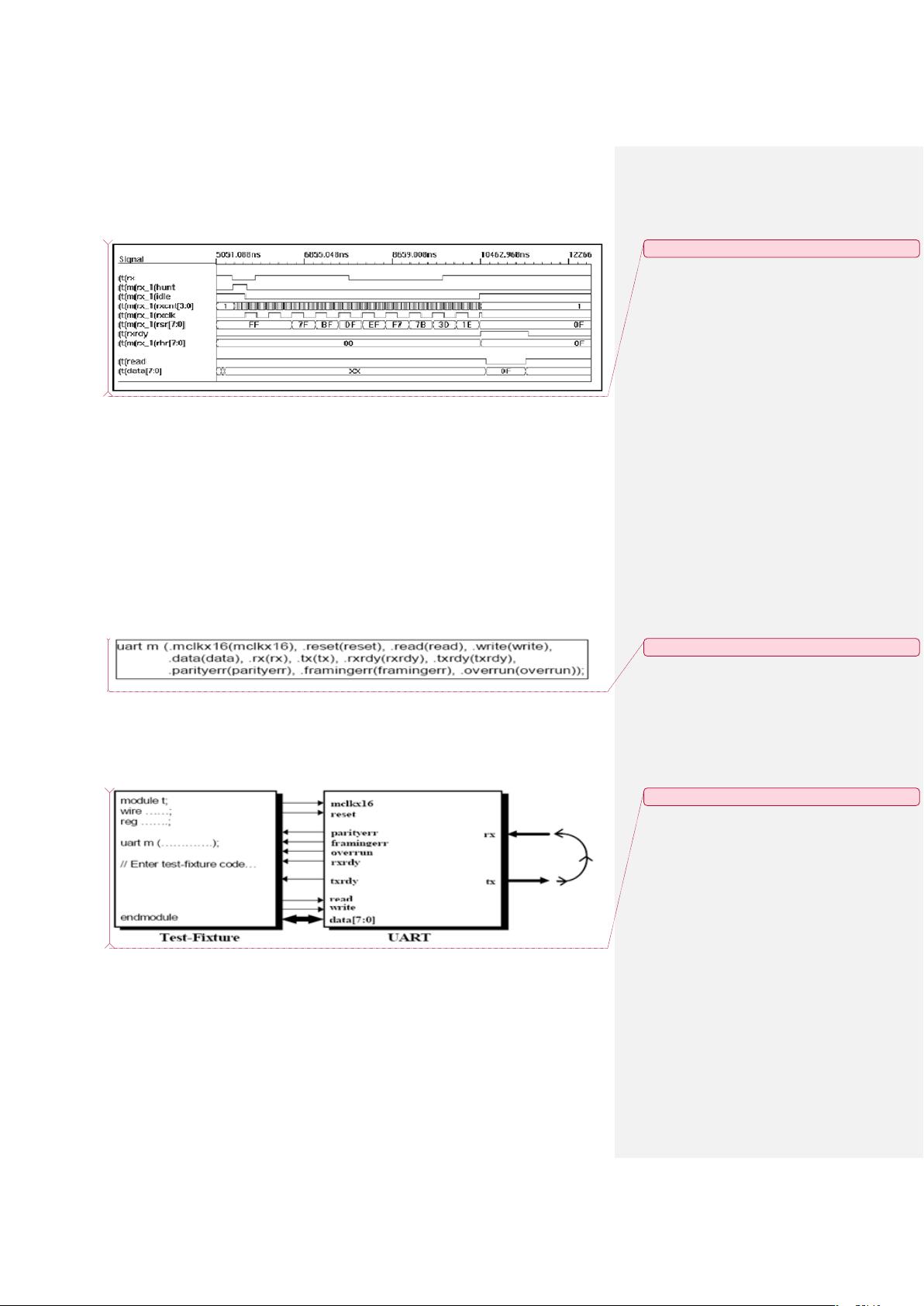

本文介绍了采用 verilog 语言对数字异步串行收发器进行设计和验证的过程。UART 通用异步串行收发器是由两个独立的 HDL 模块组成的,一个模块实现发射功能,而另一个模块实现接收功能。在顶层设计时,这两个功能模块被组合到一起,以满足通信的需要。数据通过一个双向 CPU 接口以二进制8字节的形式写入发射器,并从接收器读出。发射机和接收机之间可以通过地址映射的通道轻松建立接口。这两个模块共用一个主控时钟,该时钟为mclkx16,在每个模块内,主控时钟被分频成独立的波特率时钟。

在设计开发和验证FPGA系统时,越来越多地采用硬件描述语言HDL。行为级描述的使用不仅提高了产品的设计效率,而且在设计验证中显示出其独特的优势。Verilog和VHDL是目前最流行的HDL语言。

This article introduces the design and verification process of a digital asynchronous serial transceiver using Verilog language. The UART general asynchronous serial transceiver consists of two independent HDL modules, one module implements the transmission function, and the other module implements the reception function. These two functional modules are combined at the top-level design to meet the needs of communication. Data is written into the transmitter and read from the receiver in binary 8-byte format through a bi-directional CPU interface. Interfaces between the transmitter and receiver can be easily established through address-mapped channels. These two modules share a master control clock, which is mclkx16, and in each module, the master control clock is divided into independent baud rate clocks.

The use of behavioral-level description in FPGA system design, development, and verification has become increasingly popular. Verilog and VHDL are currently the most popular HDL languages.

The UART general asynchronous serial transceiver has the following characteristics: full-duplex operation, standard UART data frame format, even parity or odd parity mode.

Overall, this article provides a detailed overview of the design and verification process of a digital asynchronous serial transceiver using Verilog language, and highlights the benefits and unique advantages of using behavioral-level description in FPGA system development. The UART general asynchronous serial transceiver is crucial for achieving full-duplex communication and supports standard UART data frame formats with options for even or odd parity modes.

点击了解资源详情

352 浏览量

105 浏览量

2021-10-10 上传

2022-06-20 上传

166 浏览量

2023-02-20 上传

猫一样的女子245

- 粉丝: 232

最新资源

- 面向对象设计模式:提升复用与灵活性的秘籍

- SQL优化:降龙十八掌——基于索引的性能提升

- Turbo C 主菜单详解:文件与编辑操作指南

- 管理信息系统实验指南——Visual FoxPro 实践

- 深入探索:Linux内核分析技巧与实践

- iReport用户手册:Java图表开发入门

- 湖南移动通信SI合作规范:共创价值,共赢市场

- PCB编辑器网络表载入错误处理及解决方案

- C#连接DBF数据库示例与更新操作

- 持久层设计与ORM实现思想

- 构建高效统一的网络管理体系:策略与实现路径

- 中兴通讯WCDMA技术详解:从基础到演进

- 8051单片机实现简易计算器的硬件与软件设计

- 提升C编程技巧:《微软C编程精粹》精华解读

- 深入解析C/C++指针复杂类型的详细指南

- 演进式设计与计划设计:软件开发的两面