AT89C51

4

pulse is skipped during each access to external Data

Memory.

If desired, ALE operation can be disabled by setting bit 0 of

SFR location 8EH. With the bit set, ALE is active only dur-

ing a MOVX or MOVC instruction. Otherwise, the pin is

weakly pulled high. Setting the ALE-disable bit has no

effect if the microcontroller is in external execution mode.

PSEN

Program Store Enable is the read strobe to external pro-

gram memory.

When the AT89C51 is executing code from external pro-

gram memory, PSEN

is activated twice each machine

cycle, except that two PSEN

activations are skipped during

each access to external data memory.

EA

/VPP

External Access Enable. EA must be strapped to GND in

order to enable the device to fetch code from external pro-

gram memory locations starting at 0000H up to FFFFH.

Note, however, that if lock bit 1 is programmed, EA

will be

internally latched on reset.

EA

should be strapped to V

CC

for internal program

executions.

This pin also receives the 12-volt programming enable volt-

age (V

PP

) during Flash programming, for parts that require

12-volt V

PP

.

XTAL1

Input to the inverting oscillator amplifier and input to the

internal clock operating circuit.

XTAL2

Output from the inverting oscillator amplifier.

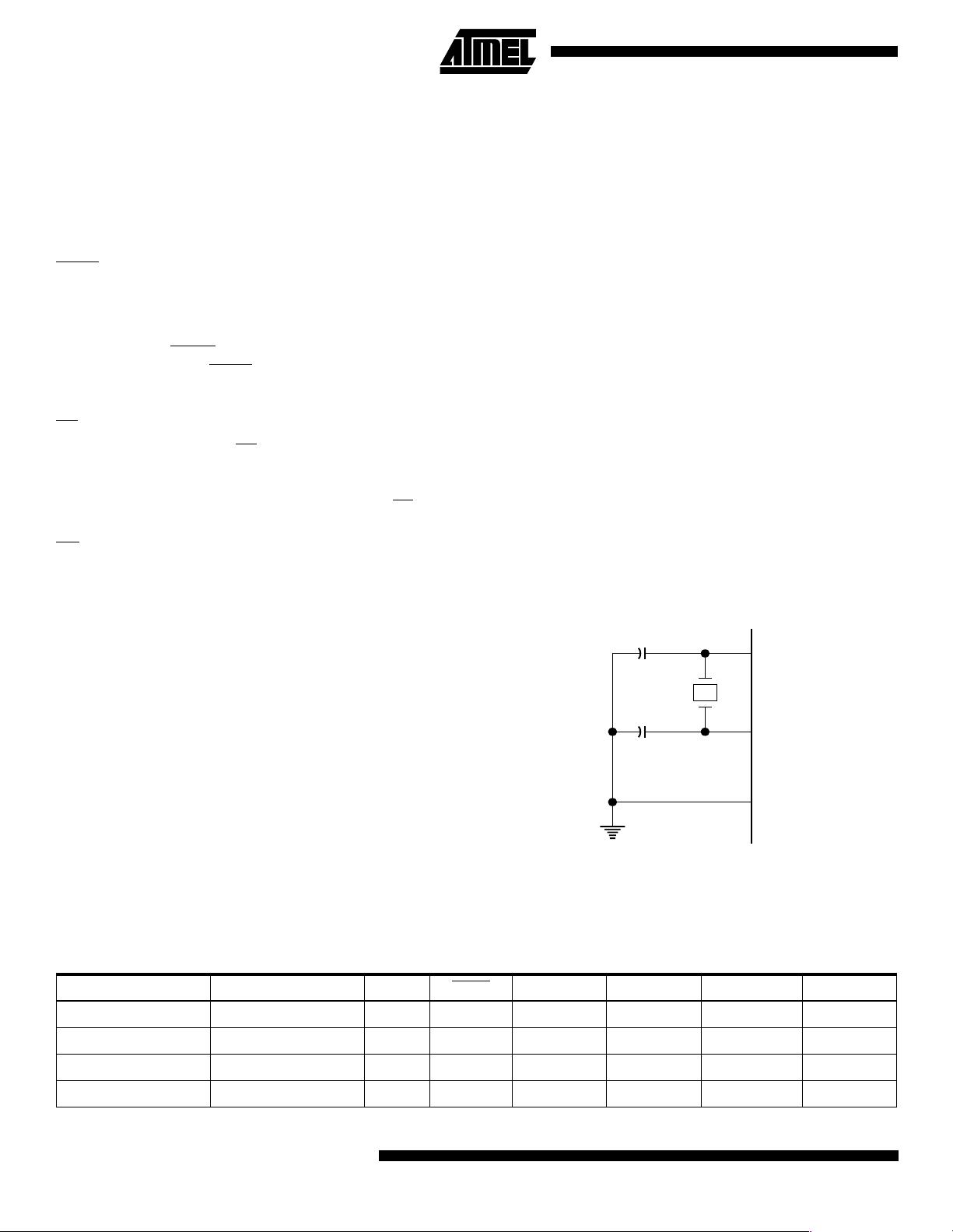

Oscillator Characteristics

XTAL1 and XTAL2 are the input and output, respectively,

of an inverting amplifier which can be configured for use as

an on-chip oscillator, as shown in Figure 1. Either a quartz

crystal or ceramic resonator may be used. To drive the

device from an external clock source, XTAL2 should be left

unconnected while XTAL1 is driven as shown in Figure 2.

There are no requirements on the duty cycle of the external

clock signal, since the input to the internal clocking circuitry

is through a divide-by-two flip-flop, but minimum and maxi-

mum voltage high and low time specifications must be

observed.

Idle Mode

In idle mode, the CPU puts itself to sleep while all the on-

chip peripherals remain active. The mode is invoked by

software. The content of the on-chip RAM and all the spe-

cial functions registers remain unchanged during this

mode. The idle mode can be terminated by any enabled

interrupt or by a hardware reset.

It should be noted that when idle is terminated by a hard

ware reset, the device normally resumes program execu-

tion, from where it left off, up to two machine cycles before

the internal reset algorithm takes control. On-chip hardware

inhibits access to internal RAM in this event, but access to

the port pins is not inhibited. To eliminate the possibility of

an unexpected write to a port pin when Idle is terminated by

reset, the instruction following the one that invokes Idle

should not be one that writes to a port pin or to external

memory.

Figure 1. Oscillator Connections

Note: C1, C2 = 30 pF ± 10 pF for Crystals

= 40 pF ± 10 pF for Ceramic Resonators

C2

XTAL2

GND

XTAL1

C1

Status of External Pins During Idle and Power-down Modes

Mode Program Memory ALE PSEN PORT0 PORT1 PORT2 PORT3

Idle Internal 1 1 Data Data Data Data

Idle External 1 1 Float Data Address Data

Power-down Internal 0 0 Data Data Data Data

Power-down External 0 0 Float Data Data Data