UMC28nm工艺下的高速JESD204B接口灵敏放大器设计

PDF格式 | 659KB |

更新于2024-08-31

| 130 浏览量 | 举报

"高速接口JESD204B的灵敏放大器设计采用了UMC 28nm CMOS工艺,旨在实现高速、低失调性能。设计中对传统的差分放大器和AB类锁存器进行了改进,提出了创新的灵敏放大器结构。通过Cadence软件进行电路设计和仿真,结果显示在1.05V电源电压、5/10GHz时钟频率下,失调电压低至0.2mV/0.8mV,传输延迟为50ps/42ps,功耗为0.37mW/0.44mW,适合作为JESD204B模数转换模块的一部分。"

在高速通信系统中,JESD204B是一种关键的接口标准,它允许高速数据传输,特别是在模数转换器(ADC)和数模转换器(DAC)之间。灵敏放大器作为其核心组成部分,其作用是捕捉微弱的模拟信号并迅速放大为可识别的数字信号,这对系统的整体性能至关重要。

在设计灵敏放大器时,主要关注以下几个关键性能指标:失调电压、速度和功耗。失调电压是衡量放大器线性度的重要参数,过大的失调可能导致信号失真。本文通过优化电路结构,降低了失调电压。速度方面,通过多相位预充和预充电模式的运用,提升了放大器的响应速度。同时,通过优化时序控制电路,减小了功耗,实现了低功耗设计。

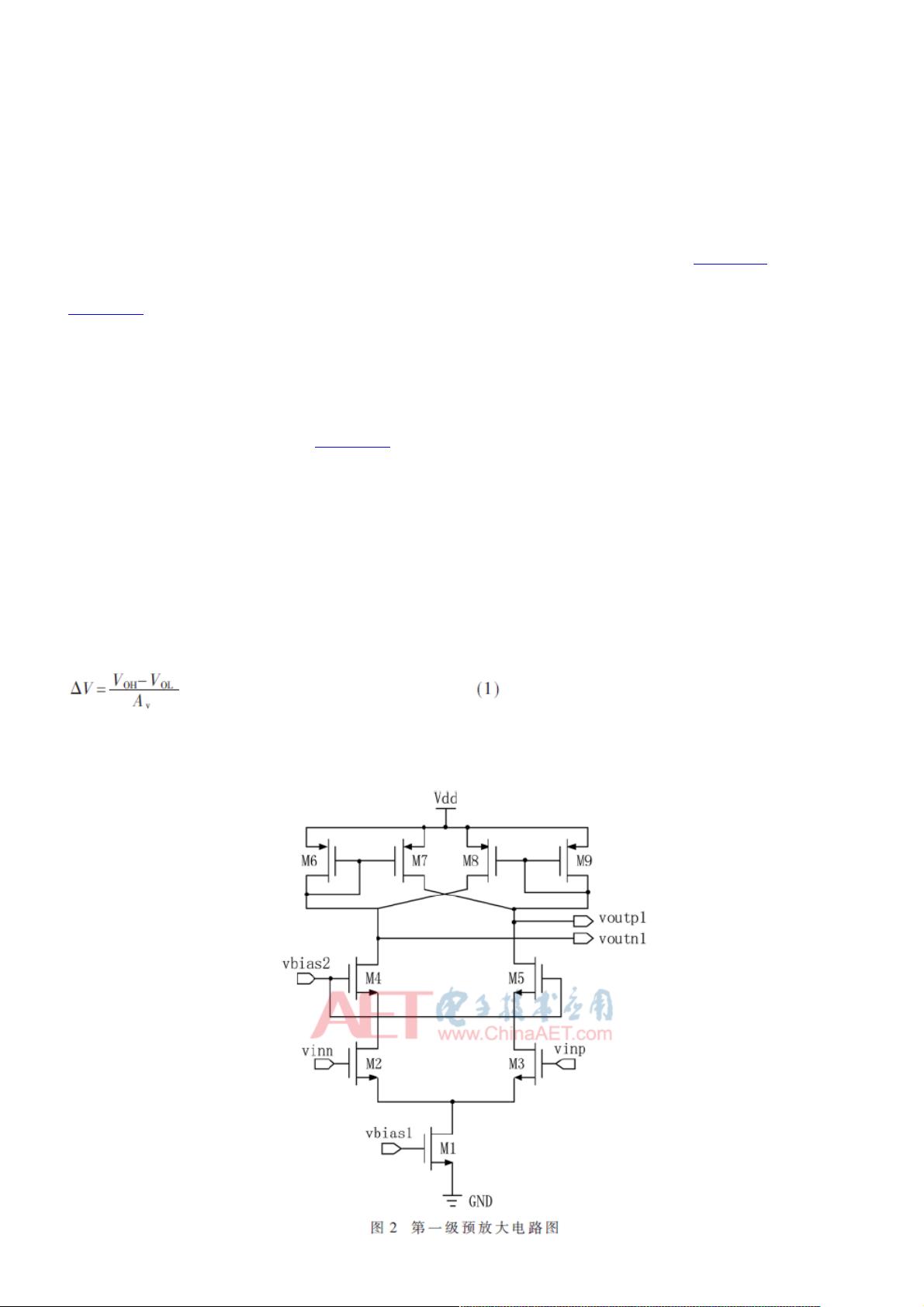

本文提出的灵敏放大器设计采用两级预放大结构,这种结构有助于在保持高速性能的同时,减少失调电压。此外,AB类锁存器的使用,结合CMOS锁存电路和SR锁存器,进一步提高了电路的稳定性和效率。当时钟信号CLK处于高电平时,电路进入复位状态,清除内部电荷,确保每次新的信号周期开始时,放大器处于已知的初始状态。而在CLK为低电平时,电路进入放大阶段,此时输入信号被放大并传递到输出。

这项工作展示了在纳米尺度工艺条件下,如何通过电路设计优化,实现高速、低失调、低功耗的灵敏放大器,满足JESD204B接口对高性能模数转换模块的需求。这样的设计方法对于未来高速接口和数据处理系统的发展具有重要的参考价值,尤其是在追求更高数据速率和更低功耗的现代通信技术中。

相关推荐

216 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

123 浏览量

105 浏览量

Yoo?

- 粉丝: 4

最新资源

- PostgreSQL 9.0 JDBC3驱动压缩包解析

- 网络时间同步程序:C#实现电脑时间精准校准

- BC3.1压缩包:C语言新手必备编程工具

- HTML5实现手机触屏滑动图片特效指南

- BDSx脚本加载器:基岩服务器的扩展解决方案

- 基于Oracle和Tomcat的Osworkflow请假系统DEMO

- 2021年Firebase火力基地项目开发实战

- C++实现反向传播神经网络及其保存功能

- 实现网页滑动门效果的DOM技术解析

- HTML5 Canvas与jQuery Jcrop实现照片剪切功能

- 软件测试基础:流程、方法与工具全面解析

- 下载分享:祈福主题ASP网站后台源码解析

- KOKO网格生成器:MATLAB实现二维有限元网格生成

- Linux中文输入法软件:高效中文输入解决方案

- 超市收银系统VB前端开发源码

- 精选jQuery文字图片滚动代码下载