Compact SiPM based Detector Module for

Time-of-Flight PET/MR

Michael Ritzert, Peter Fischer, Viacheslav Mlotok, Ivan Peri, Claudio Piemonte, Nicola Zorzi, Volkmar Schulz,

Torsten Solf, and Andreas Thon

Abstract—We present a compact detector module for γ de-

tection in the PET part of a simultaneous ToF-PET/MR system.

The module covers an area of 3.3 cm × 3.3 cm with 64 SiPM

based readout channels. It is composed of a stack of three PCBs of

identical size: The SiPMs on the topmost PCB are read out by two

full-custom ASICs located on a second PCB located underneath.

A third PCB at the bottom of the stack contains a local voltage

regulator, an FPGA for ASIC control and data processing, and

DACs to generate bias voltages for the readout ASICs and the

SiPM devices. An LYSO scintillator block is optically coupled to

the SiPMs for gamma to light conversion.

I. INTRODUCTION

T

HERE are numerous challenges in implementing a PET

detector system for use in an MR scanner. The system

must not only be small to fit inside the scanner, it must also

operate in a hostile environment, withstanding MR gradients,

HF injections and vibrations from the operation of the MR

system. Photomultiplier tubes as currently used in most PET

systems, cannot be operated in a magnetic field. Systems using

light guides to direct the scintillation light outside the B field

have been proposed [1]. This approach allows for the use of

conventional and readily available electronics. It suffers from

a bad light yield, however. Other proposed systems [2] put MR

hard avalanche photo diodes and preamplifiers in the scanner

and connect them to readout electronics outside. A large

number of analog connections are susceptible to noise pickup

from MR operation, however. With the required shielding, they

take up precious space in the scanner, so that this approach is

not scalable towards large, full body rings.

Our approach is to integrate the full acquisition chain (light

detection, amplification, digitization, time stamping, control)

into compact multi channel modules located inside the scanner

volume. The interface to the outside world consists of only few

data and control connections, power and cooling.

The following section II describes the PCB stack in detail.

First measurements will be presented in section III.

Manuscript received June 14, 2009. This work was supported by the

European Union under Grant No. 2016511.

M. Ritzert, P. Fischer, V. Mlotok and I. Peri are with the

University of Heidelberg, 69117 Heidelberg, Germany (e-mail:

michael.ritzert@ziti.uni-heidelberg.de; peter.fischer@ziti.uni-heidelberg.de;

viacheslav.mlotok@ziti.uni-heidelberg.de; ivan.peric@ziti.uni-heidelberg.de).

C. Piemonte and N. Zorzi are with Fondazione Bruno Kessler, 38050

Trento, Italy (e-mail: piemonte@fbk.eu; zorzi@fbk.eu).

V. Schulz, T. Solf and A. Thon are with Philips Research Eu-

rope, 52066 Aachen, Germany (e-mail: volkmar.schulz@philips.com;

torsten.solf@philips.com; andreas.thon@philips.com).

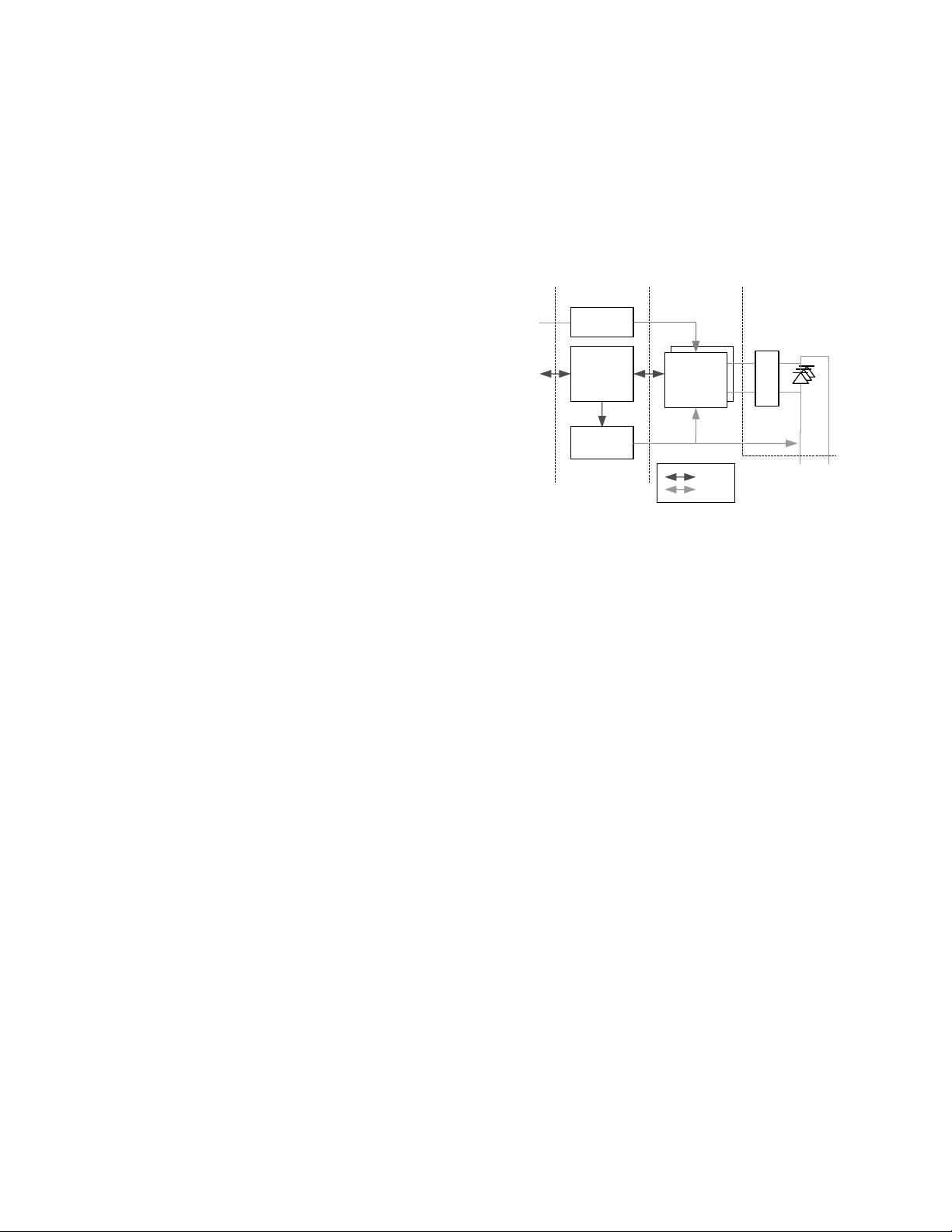

to DAQ

Impedance

Matching

Readout

ASIC

FPGA

DACs

3

rd

PCB 2

nd

PCB 1

st

PCB

digital

analog

to HV

supply

LDO

Power

Fig. 1. Block diagram of the detector stack.

II. IMPLEMENTATION

The basic concept of the design is to use highly integrated

electronics in order to minimize the number of components

required. Pursuing a modular design approach, different tasks

in the detection chain are distributed among different PCBs.

In total, there are three PCBs, each 3.3 cm × 3.3 cm in size,

stacked on top of each other. The high density connectors used

to bring the signals from one PCB to the next require a non-

negligible area, but they simplify the implementation of design

variations in this first design iteration. A simple block diagram

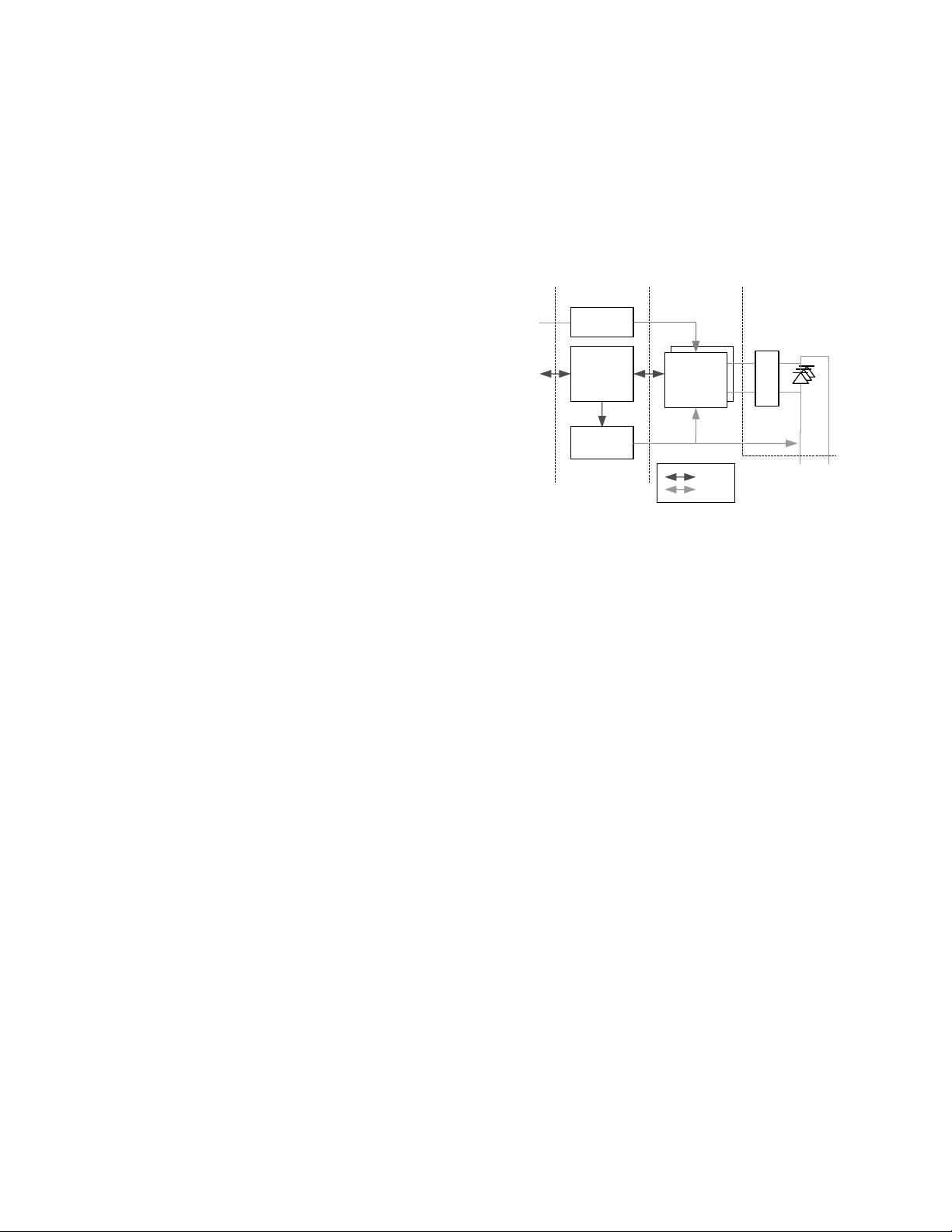

of the stack is shown in Fig. 1, Fig. 2 shows a photograph of

the four-side buttable stack. The details of each PCB will be

discussed below.

A. SiPM Board

The entire surface of the topmost PCB is covered with

64 SiPM based readout channels. Each SiPM measures

4 mm × 4 mm. To reach a high fill factor, four SiPMs have

been integrated onto a large monolithic piece of silicon as 2×2

arrays. A geometric fill factor of 84 % could be realized this

way.

All passive components required to interface the SiPMs

to the ASICs are placed on the bottom side of this PCB.

Currently, several connection schemes between the SiPMs

and the ASIC are under investigation. Variations of DC and

AC coupled designs as well as single-ended and differential

readout are implemented. Some variations allow for fine tuning

of the HV brought in through the connector stack by means

of a DAC on the Interface board. In addition, a temperature

sensor is present on the PCB.

2009 16th IEEE-NPSS Real Time Conference

978-1-4244-4455-7/09/$25.00 ©2009 IEEE

Authorized licensed use limited to: Huazhong University of Science and Technology. Downloaded on December 16, 2009 at 07:08 from IEEE Xplore. Restrictions apply.