视频ADC中的关键:线性锁相环设计与模拟

需积分: 10 128 浏览量

更新于2024-09-11

收藏 92KB PDF 举报

视频ADC(Analog-to-Digital Converter)中的锁相环(Phase-Lock Loop, PLL)是一种至关重要的电路组件,它在现代电子系统中扮演着基石角色。PLL被广泛应用于通信、多媒体和其他众多应用领域,其理论和数学模型主要分为线性和非线性两种。尽管非线性理论通常更为复杂,但在实际设计中,线性理论由于其简洁性和易于处理而被广泛应用。

本文由Wen Li,高级系统工程师,以及Jason Meiners,混合信号产品组设计经理,来自德克萨斯仪器公司撰写。他们强调,对于模拟PLL,线性控制理论已经提供了相当精确的模型,只要满足特定条件,这一模型在大多数电子应用中是足够的。文章从连续时间域的一个明确模型出发,介绍了一种基于同样线性控制理论的数字PLL建模和设计方法。

图1展示了德州仪器公司的THS8083混合信号器件,该器件针对液晶显示器(LCD)和数字电视(DTV)应用。PLL在这些设备中的任务是根据输入信号恢复像素时钟。在视频ADC中,PLL确保了数据采样与视频信号的同步,这对于保持视频质量、消除失真以及实现高采样率至关重要。

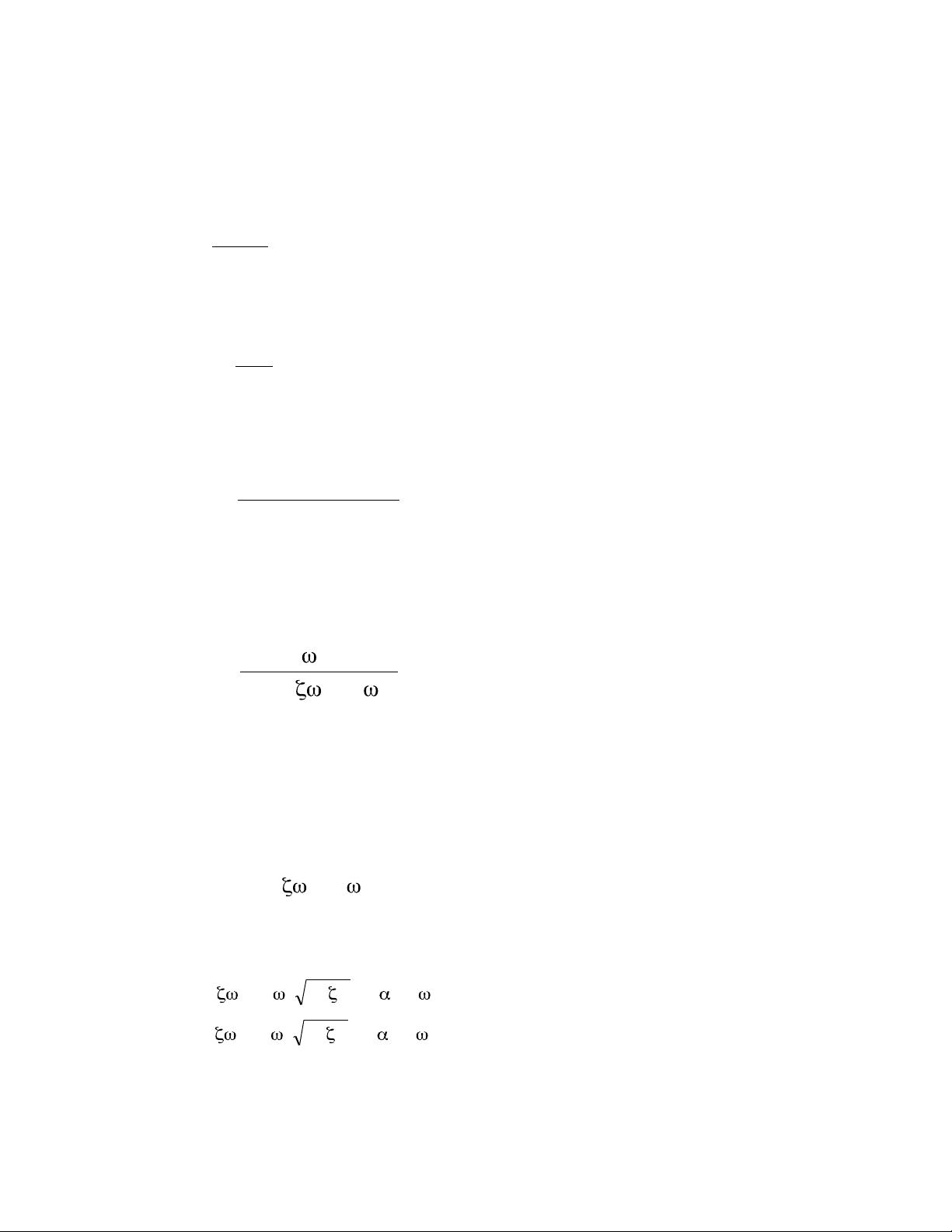

设计一个有效的视频ADC中的PLL,需要考虑的关键参数包括锁定速度、锁定范围、噪声抑制能力和动态性能。线性模型在此过程中起着决定性作用,设计师需要对闭环系统的开环增益、相位裕度和锁定频率特性有深入理解。此外,数字PLL可能涉及混频器、分频器、电压控制振荡器(VCO)、相位检测器以及反馈路径等元件,每个部分都需要精心设计以达到最佳性能。

文章可能会进一步探讨PLL的设计步骤,包括选择合适的锁定策略(自启动或外同步),确定参考频率和参考电压,以及如何调整控制算法以适应不同的信号条件。还会讨论PLL的噪声分析,如何通过噪声转移函数来减小锁定误差,并优化环路滤波器的设计以减少环路带宽内的噪声引入。

总结来说,视频ADC中的锁相环是一个复杂的但至关重要的系统,其性能直接影响到视频信号的精度和稳定性。通过运用线性控制理论,设计者能够高效地开发出适应各种应用场景的PLL解决方案。对于电子工程师而言,深入理解并掌握PLL的工作原理和设计技巧,是提升ADC整体性能的关键。

3734 浏览量

225 浏览量

2021-07-26 上传

2022-11-27 上传

2022-12-03 上传

162 浏览量

2022-12-03 上传

memsensors

- 粉丝: 0

最新资源

- Web远程教学系统需求分析指南

- 禅道6.2版本发布,优化测试流程,提高安全性

- Netty传输层API中文文档及资源包免费下载

- 超凡搜索:引领搜索领域的创新神器

- JavaWeb租房系统实现与代码参考指南

- 老冀文章编辑工具v1.8:文章编辑的自动化解决方案

- MovieLens 1m数据集深度解析:数据库设计与电影属性

- TypeScript实现tca-flip-coins模拟硬币翻转算法

- Directshow实现多路视频采集与传输技术

- 百度editor实现无限制附件上传功能

- C语言二级上机模拟题与VC6.0完整版

- A*算法解决八数码问题:AI领域的经典案例

- Android版SeetaFace JNI程序实现人脸检测与对齐

- 热交换器效率提升技术手册

- WinCE平台CPU占用率精确测试工具介绍

- JavaScript实现的压缩包子算法解读