"Verilog HDL语言设计MIPS 54条指令单周期CPU实现及功能验证"

需积分: 0 190 浏览量

更新于2024-03-15

收藏 4.52MB PDF 举报

根据上述要求,本文将详细介绍MIPS 54条指令单周期CPU设计的相关内容。首先,我们将按照实验目标和总体设计要求逐步展开描述,包括使用Verilog HDL语言实现CPU的设计和仿真,实现54条MIPS指令的功能,以及处理边界数据和复杂随机指令序列的能力等。

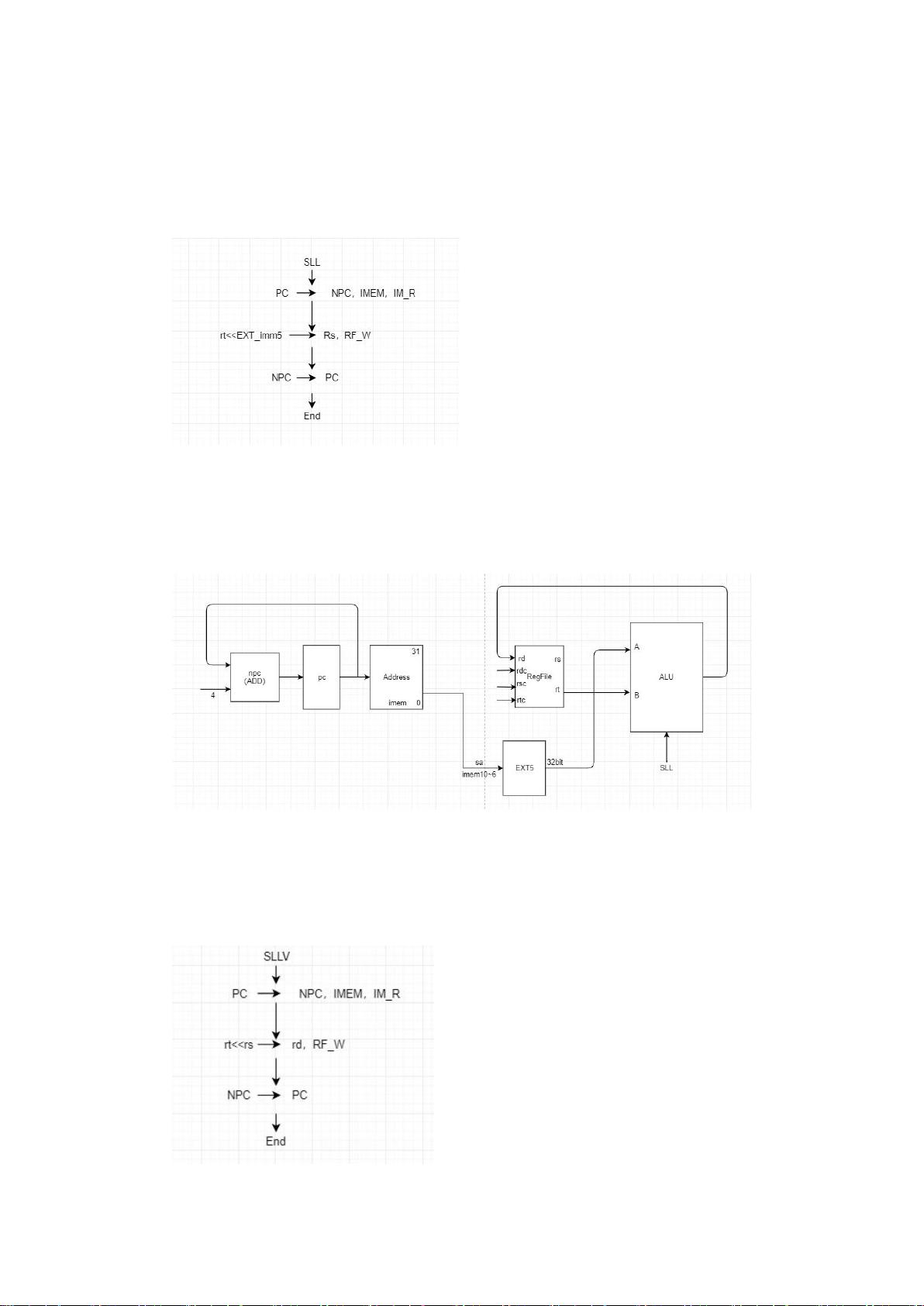

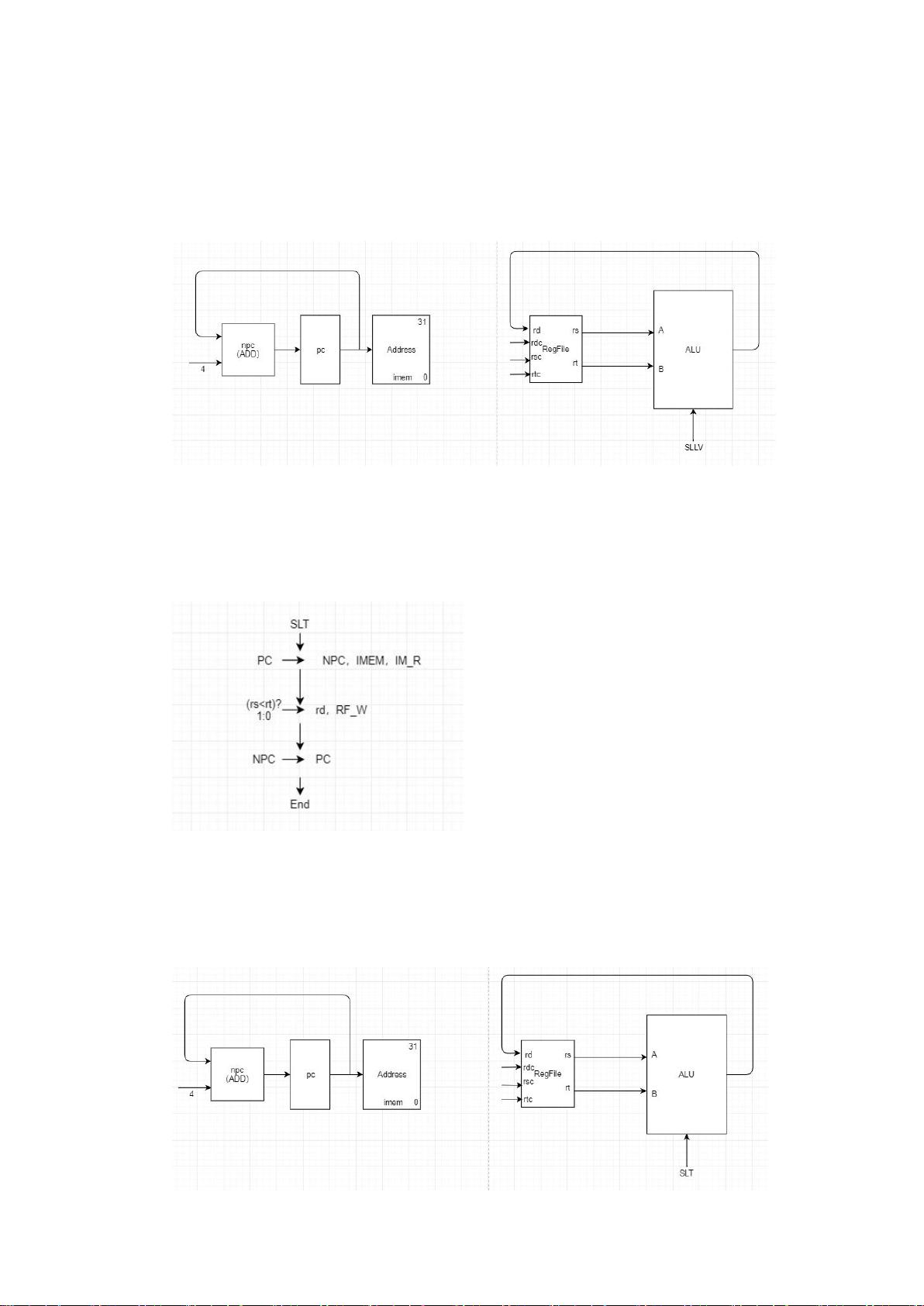

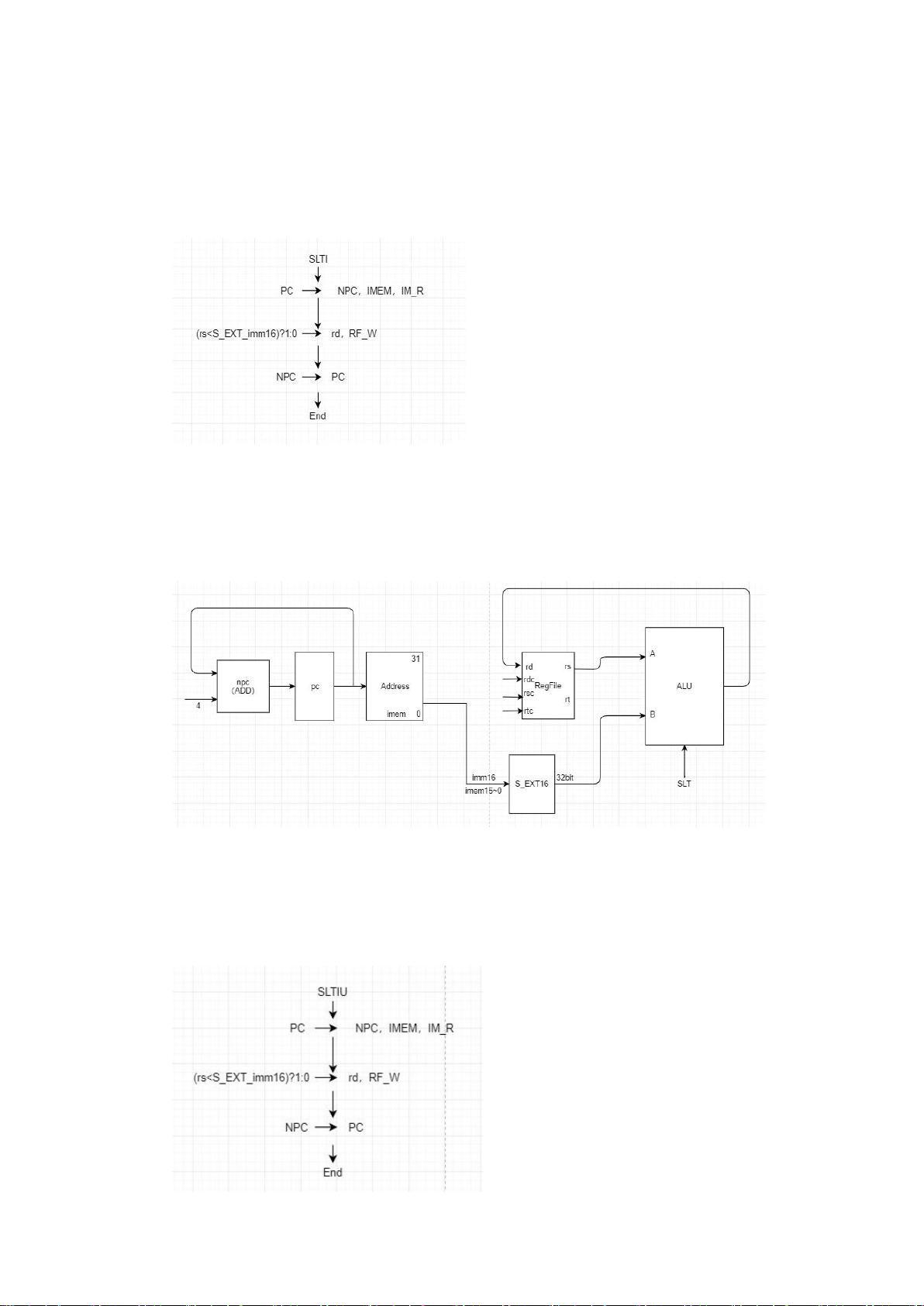

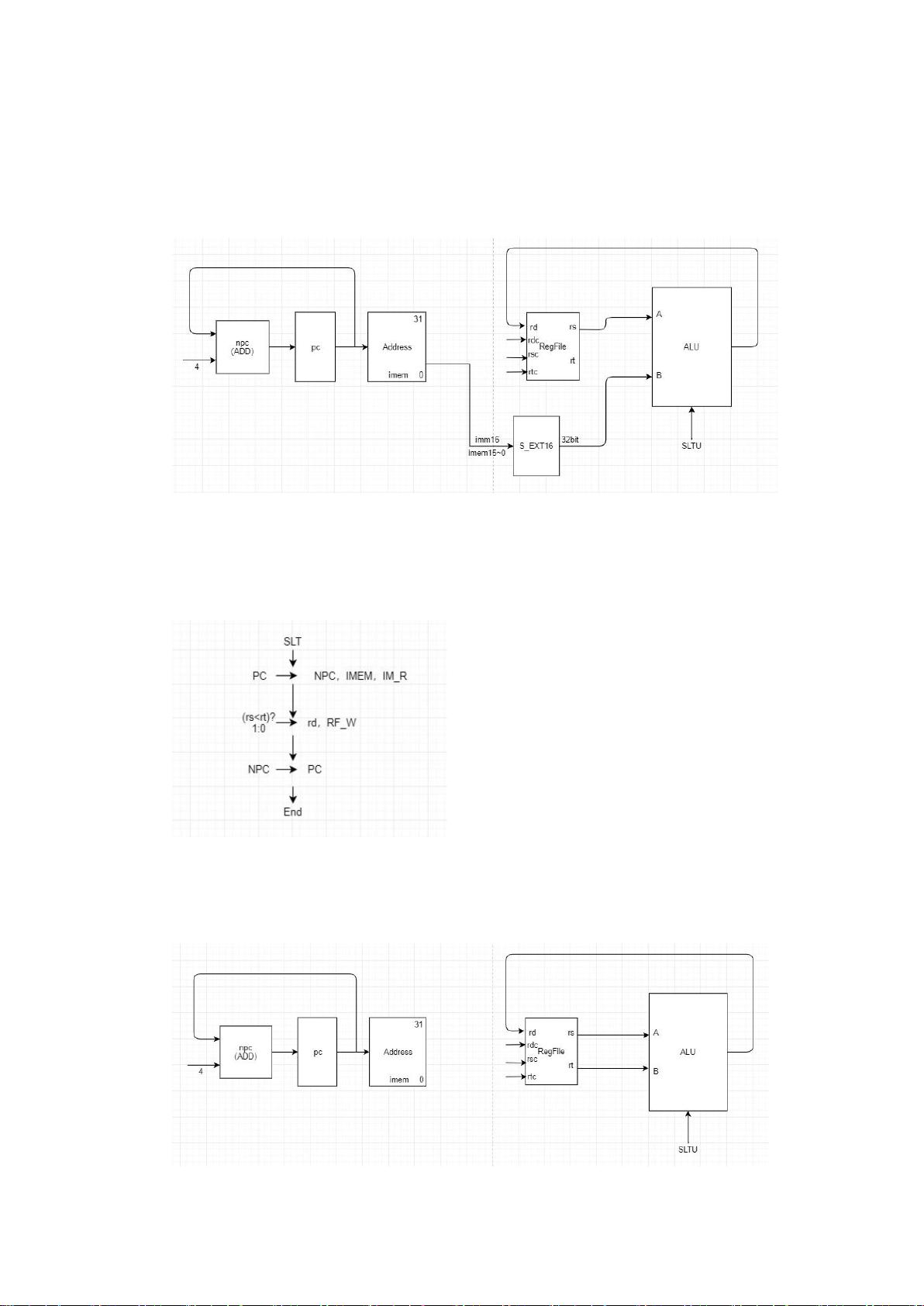

在实现MIPS 54条指令的CPU设计中,首先需要分析每条指令的操作和所需的器件。以ADD指令为例,我们需要取指令、将寄存器中的数值相加并存入目标寄存器、然后更新PC寄存器。因此,ADD指令需要PC寄存器和指令存储器这两个器件来完成相应的操作。在总体设计中,我们还需要考虑其他53条指令的种类、名称、格式和功能,以确保CPU设计的完备性和正确性。

然后,我们将根据各条指令的设计要求逐一实现。对于ADD指令,我们需要确保能够正确执行相应的操作并更新寄存器中的数值。在设计过程中,我们需要考虑如何处理边界指数据以及复杂的随机指令序列,确保CPU能够正确运行并执行相应的功能。此外,我们还需要使用提供的COE文件来初始化IP核的数据寄存器,并确保CPU能够正确执行每一条指令,达到COE文件所代表的程序的预期结果,同时能够通过网站上的测试。

总的来说,在实现MIPS 54条指令的CPU设计中,需要深入理解CPU的原理,并绘制出设计的通路图。同时,使用Verilog HDL语言设计实现CPU的过程中,需要确保各个功能模块的正确性和协调性,以使CPU能够正确执行各种指令并达到设计的预期功能。通过对每条指令的设计和实现,以及对边界数据和复杂随机指令序列的处理能力,我们可以使CPU设计达到高效、稳定和可靠的水平。

综上所述,通过本文的描述和总结,我们可以清晰了解MIPS 54条指令单周期CPU设计的相关内容,以及设计过程中的各项要求和挑战。通过严格按照要求逐步实现各项功能,我们可以设计出一个能够正确执行各种指令并保证高效性和稳定性的CPU。这对于深入理解CPU的工作原理和提高硬件设计水平具有重要意义。

2017-10-23 上传

2022-08-03 上传

2022-09-14 上传

2022-09-21 上传

2019-03-25 上传

2021-05-12 上传

点击了解资源详情

2023-03-03 上传

艾苛尔

- 粉丝: 35

- 资源: 306

最新资源

- Aspose资源包:转PDF无水印学习工具

- Go语言控制台输入输出操作教程

- 红外遥控报警器原理及应用详解下载

- 控制卷筒纸侧面位置的先进装置技术解析

- 易语言加解密例程源码详解与实践

- SpringMVC客户管理系统:Hibernate与Bootstrap集成实践

- 深入理解JavaScript Set与WeakSet的使用

- 深入解析接收存储及发送装置的广播技术方法

- zyString模块1.0源码公开-易语言编程利器

- Android记分板UI设计:SimpleScoreboard的简洁与高效

- 量子网格列设置存储组件:开源解决方案

- 全面技术源码合集:CcVita Php Check v1.1

- 中军创易语言抢购软件:付款功能解析

- Python手动实现图像滤波教程

- MATLAB源代码实现基于DFT的量子传输分析

- 开源程序Hukoch.exe:简化食谱管理与导入功能