SRAM工艺FPGA的加密策略与保密挑战

PDF格式 | 202KB |

更新于2024-08-30

| 46 浏览量 | 举报

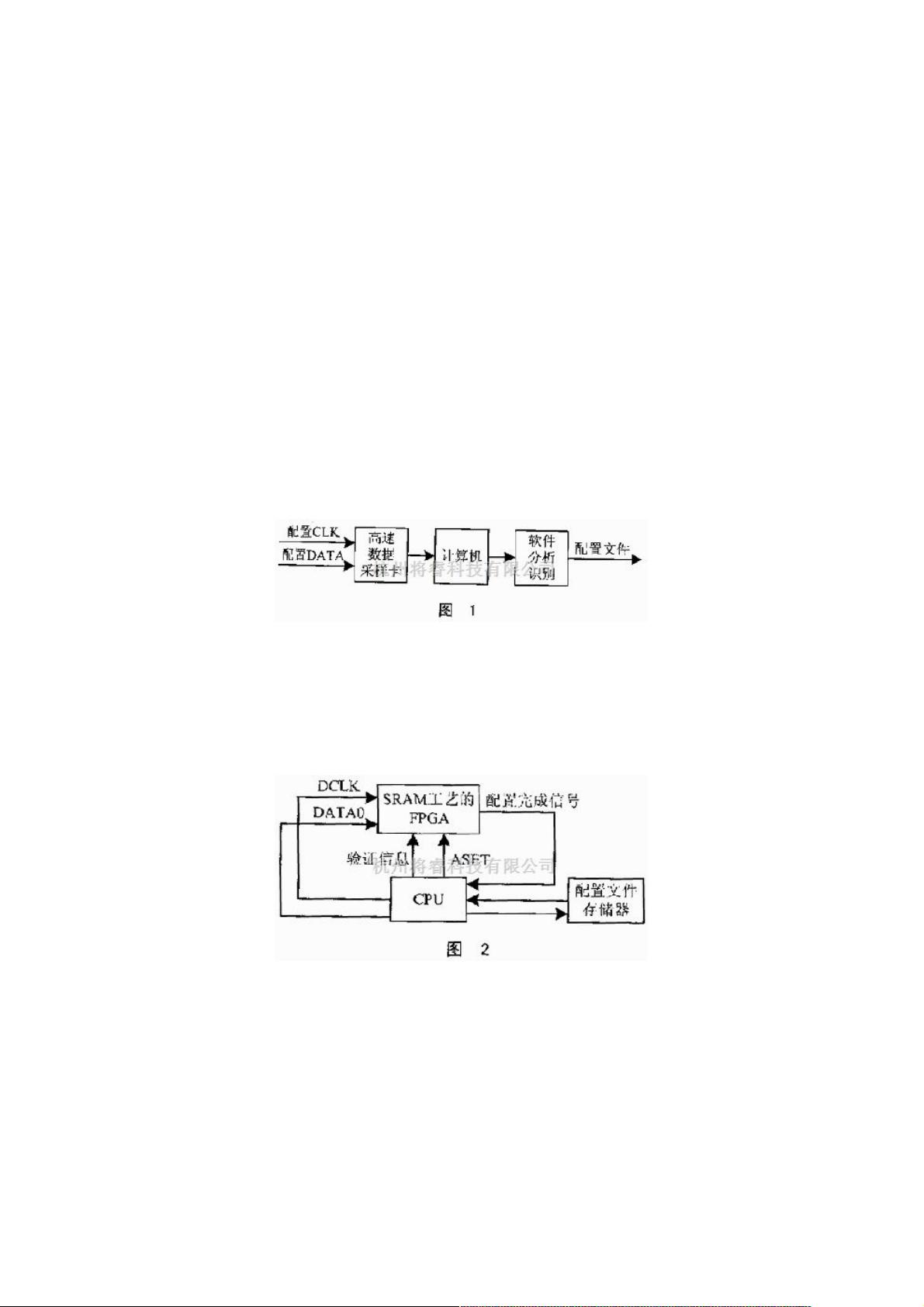

在现代电子系统设计中,基于单片机SRAM工艺的FPGA因其高性能和可升级性备受青睐,但这种工艺也带来了一定的安全隐患。由于FPGA在上电时需要进行重配置,这使得其配置的位数据流可能被监控并用于克隆设计,威胁到设计者的知识产权。针对这个问题,本文主要探讨了基于SRAM工艺的FPGA的保密性挑战以及有效的加密策略。

首先,SRAM工艺FPGA的配置方式主要包括三种:通过计算机下载电缆配置、专用配置芯片如Altera EPCX系列、以及存储器加微控制器的方法。前两者主要用于设计调试,而后者在实际产品中更为常见,因为它们具有简单外围电路、体积小、成本低且易于升级的特点。

然而,这些配置过程都涉及到将配置数据写入FPGA的SRAM区域,这意味着只要能正确捕获和解析这些数据,就可以进行克隆。为了防止这种未经授权的复制,必须采取加密措施。传统的单片机加密仅限于外部数据流,不足以阻止内部电路的复制,因为FPGA供应商并未公开位数据流的具体定义。

有效的加密方法需要针对这个特性进行设计。一种可能的策略是采用硬件加密技术,比如在FPGA内部集成专用的加密引擎,对配置数据进行实时加密处理。这样,即使外部能够获取到配置数据,也无法解密出实际的电路设计。另一种方法是采用软件加密,通过嵌入自加密算法或使用预置的密钥,使得每个FPGA在上电后只有在特定条件下才能解密并配置。

此外,还可以考虑采用动态加密策略,例如在每次配置时生成一个新的密钥,或者使用一次性可编程(OTP)存储器来存储加密密钥,确保每次上电时使用不同的密钥,增加破解的难度。同时,结合物理安全措施,如封装设计上的防拆卸标记,可以进一步增强加密的防护效果。

针对基于单片机SRAM工艺的FPGA的加密应用,需要综合运用硬件和软件加密手段,以及物理层面的防护措施,确保设计者的知识产权在产品生命周期内得到充分保护。随着技术的进步,未来可能会出现更高级别的加密技术,以适应不断发展的电子系统安全需求。

相关推荐

weixin_38646706

- 粉丝: 4

最新资源

- 网页自动刷新工具 v1.1 - 自定义时间间隔与关机

- pt-1.4协程源码深度解析

- EP4CE6E22C8芯片三相正弦波发生器设计与实现

- 高效处理超大XML文件的查看工具介绍

- 64K极限挑战:国际程序设计大赛优秀3D作品展

- ENVI软件全面应用教程指南

- 学生档案管理系统设计与开发

- 网络伪书:社区驱动的在线音乐制图平台

- Lettuce 5.0.3中文API文档完整包下载指南

- 雅虎通Yahoo! Messenger v0.8.115即时聊天功能详解

- 将Android手机转变为IP监控摄像机

- PLSQL入门教程:变量声明与程序交互

- 掌握.NET三层架构:实例学习与源码解析

- WPF中Devexpress GridControl分组功能实例分析

- H3Viewer: VS2010专用高效帮助文档查看工具

- STM32CubeMX LED与按键初始化及外部中断处理教程