使用3-8译码器和与非门设计数字逻辑电路

版权申诉

199 浏览量

更新于2024-07-03

收藏 663KB PPT 举报

"该教学课件主要探讨了数字逻辑设计中的数选、分配以及奇偶校验相关的概念,适用于计算机科学和互联网领域的学习者。通过课件内容,我们可以了解到如何利用3线-8线译码器和逻辑门设计特定的逻辑电路。其中,课件包含了两个具体的练习题目,一个是用3-to-8译码器和逻辑门实现特定的逻辑函数F,另一个是设计一个基于3个按键的密码锁逻辑电路。此外,课件还涵盖了优先编码器74x148的使用以及三态缓冲器的概念,这些都是数字逻辑系统设计中的重要组成部分。"

在数字逻辑设计中,数选和分配是基本操作,通常通过译码器来实现。3-to-8译码器是一种多路选择器,它可以根据输入的三位二进制代码,从八个输出中选择一个进行激活。在这个例子中,任务是用3-to-8译码器和逻辑门实现逻辑函数F,其函数表示为F=∑xyz(1,3,6,7)。这意味着当输入的x,y,z取值为100,011,110,111时,F的输出为1,其他情况为0。

密码锁的逻辑设计是一个实际应用的例子,它要求在不同的按键组合下产生不同的响应。这个设计需要使用3线-8线译码器和与非门,通过译码器的输出和与非门的组合,可以实现各种按键组合下的逻辑功能。例如,当没有按键按下时,译码器的使能输入EN为0,所有输出均为高阻态,即不打开锁也不报警;当只有一个键按下时,EN为1,但与非门的输出为0,导致锁不打开且发出警报;当有两个键按下时,EN和特定的译码器输出组合使得锁打开;而当三个键都按下时,锁会打开并报警。

课件还提到了优先编码器74x148,这是一种能够识别并编码多个输入中最高优先级信号的器件。当没有输入请求时,使能输出EO低电平有效,表示没有活动的输入;如果有输入请求,EO变为高电平,同时根据输入的优先级,选通输出GS表示哪个输入具有最高优先级。在级联多个74x148以处理更多的输入请求时,使能输入EI和组选通输出GS起着关键作用。

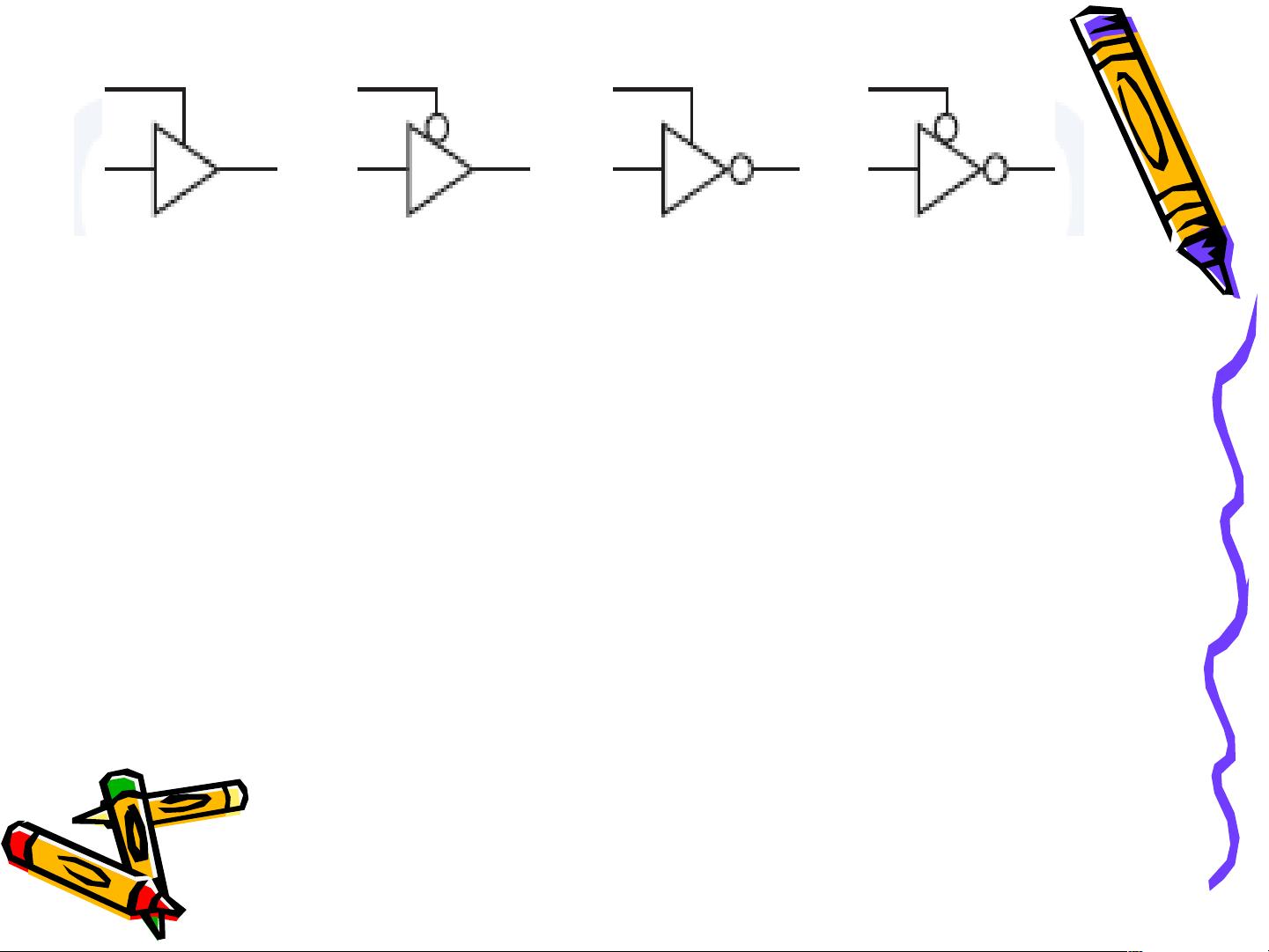

最后,三态缓冲器是数字系统中用于数据传输的重要元件,它可以控制其输出端口是否能够向总线或其他设备提供数据。三态缓冲器的启用由一个附加的使能输入控制,当使能输入为有效状态时,缓冲器允许数据通过;反之,当使能输入无效时,输出进入高阻态,不连接到总线,避免干扰其他设备的信号。

通过这些内容的学习,学生可以深入理解数字逻辑设计的基本原理,并掌握如何将这些原理应用于实际问题的解决中。

2021-09-21 上传

2021-09-21 上传

116 浏览量

2022-06-29 上传

2022-06-29 上传

2022-06-16 上传

2022-05-08 上传

2021-09-23 上传